Validation Expérimentale

Introduction

Dans le but de valider expérimentalement notre réseau de communication, nous présentons, dans ce chapitre, une proposition d’architecture compl`ete avec les unités de routage (SGM et DFR) et le syst`eme mémoire (FBS) proposés dans cette th`ese. Cette architecture exploite différentes unités de calculs dédiées afin de réaliser des exemples d’applications concr`etes en vision embarquée, développées au sein du CE-CTP de Sagem. Cette architecture, que nous appelons Multi Data Flow Ring (MDFR), utilise une topologie du réseau en anneau, couplée `a un syst`eme de mémoire de trames [19, 20]. La premi`ere partie de ce chapitre présente le choix topologique ainsi que la description de l’architecture. Les méthodes de chargement dynamique d’un contexte et de configuration des unités de calculs sont également décrites. Dans une seconde partie, nous présentons des résultats d’implémentation sur un FPGA avec une évaluation en surface et en temps dans le cadre d’une application concr`ete pour la restitution d’image bi-capteurs.

Architecture Multi Data Flow Ring

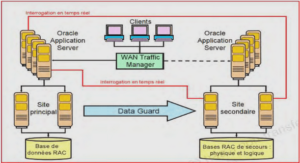

Dans notre réseau, la topologie globale est fixée par les routeurs maˆıtres (SGMs) qui sont reliés entre eux par un nombre variable de routeurs esclaves (DFRs). 194 Validation Expérimentale Chapitre 7. Afin de valider notre proposition, nous choisissons une topologie en anneau permettant d’implémenter le plus simplement et efficacement possible des applications orientées flot de données, comme celles présentées au chapitre 2. Pour cette topologie, notre proposition de description des instructions dans les en-tˆetes se prˆetent idéalement `a des opérations récursives du fait de la présence d’un champ dédiée au nombre d’itérations nécessaires pour une opération donnée.

Présentation de l’architecture MDFR

Nous proposons ainsi l’architecture Multi Data Flow Ring (MDFR) présentée en figure 7.1. PE 0 PE K PE K+1 PE N PE M+1 PE L+1 FBS PE L PE M Pixel Stream out Pixel Stream in Pixel Stream in Pixel Stream out Pixel Stream out Pixel Stream in I/O GATE DFR 0 FRAME SERVER Pixel Stream out Pixel Stream in 2 2 DP CTR DFR K DP CTR DFR N DP CTR DFR M+1 DP CTR DFR K+1 DP CTR DFR L DP CTR DFR M DP CTR DFR L+1 DP CTR SGM 3 Adaptable Datapath Memory Controller DP CTR M CTR 2 Datapath Controller LMS 2 2 DP CTR M CTR LMS LMS LMS M CTR DP CTR M CTR DP CTR M CTR DP CTR FRAME MEMORIES DP CTR M CTR 3 3 3 3 3 3 3 3 U CTR Unit Controller U CTR U CTR U CTR U CTR Read / Write Command 4 1 3 Figure 7.1: Architecture du Multi Data Flow Ring Cette architecture est basée sur notre réseau de communication, organisé suivant une topologie en anneau de routeurs maitres (SGMs) et esclaves (DFRs). Les routeurs sont interconnectés suivant 4 voies de communications unidirectionnels : 2 voies orientées dans le sens des aiguilles d’une montre et les 2 autres voies dans le sens inverse. Cette configuration offre la possibilité au paquet de données de transiter dans les deux sens de circulation, ce qui lui permet ainsi d’atteindre un routeur maˆıtre de destination avec le Chapitre 7. Validation Expérimentale 196 plus court chemin possible. Elle permet également au DFR d’utiliser le mode d’exécution parall`ele dans les deux sens. Les routeurs maˆıtres (SGMs) contiennent le contexte de l’application et contrˆolent les mouvements principaux des flux de pixels. Nous rappelons que ce sont les seuls routeurs `a ˆetre dotés d’interfaces d’entrée et de sortie de données. Afin de pouvoir exploiter l’architecture, tous les nouveaux flux de pixels `a traiter, provenant d’une source, sont préalablement paquetisés avec un en-tˆete. Cet en-tˆete contient au minimum l’attribut de l’image décrivant le type de source et une information d’adressage indiquant la position de l’afficheur de sortie souhaité dans le réseau. Cette position correspond `a celle du SGM sur lequel l’afficheur est relié en sortie. Un SGM fournit alors `a tout nouveau paquet de donnée entrant, un ensemble d’opération de traitement `a appliquer, suivant le contexte de l’application associée `a la source de pixel detectée. Les SGMs s’échangent mutuellement des paquets de données sur un réseau linéaire de routeurs esclaves (DFRs) dont le rˆole est d’adapter le chemin de données suivant les modes d’exécution des opérations, spécifiés dans l’en-tˆete du paquet de données. Le paquet de données ne peut sortir du syst`eme que lorsque toutes les opérations nécessaires ont été appliquées et qu’il a atteint le SGM de destination. Le fonctionnement de l’architecture peut ˆetre compris par analogie `a un réseau ferroviaire composé de gares principales (SGMs) et de stations intermédiaires (DFRs) séparant les gares. Un paquet de donnée peut s’apparenter `a un train composé d’un chargement d’éléments `a traiter. Chaque train entrant circule d’une gare de départ vers une gare de destination. Une feuille de route est fournie `a la gare de départ contenant la gare de destination ainsi qu’un ensemble de traitement `a appliquer `a son chargement. L’architecture MDFR peut ˆetre paramétrée avant synth`ese suivant le nombre de SGMs et de DFRs. Afin de garantir le maximum de bande passante `a la fois en traitement sur le réseau et en acc`es sur le syst`eme de mémoire FBS, nous limitons le nombre de SGMs `a 4. Cette architecture autorise ainsi l’interfa¸cage de 4 sources d’images et de 4 afficheurs en sortie. Par ailleurs, avec les 4 voies de communications du syst`eme, les flux de pixels de chaque capteur peuvent ainsi transiter avec le maximum de bande de passante sur des lignes individuelles entre les SGMs.