Système de mémorisation dynamiquement adaptable

Dans un système de vision embarquée, nous appelons généralement par le terme Frame Buffer [146], un espace de mémorisation dédié au stockage de différentes trames d’image. Ces trames peuvent provenir soit directement des capteurs,

ou ˆetre le résultat d’opé rations effectuées par des unités de calcul. Le Frame Buffer est un élément clef des architectures de vision embarquée [7] et son utilisation est incontournable pour la syn chronisation de différents flux de données `a des cadencements différents [147].

Il peut ˆetre requis tout au long d’une chaˆıne de traitement aussi bien en amont pour l’acquisition des images qu’en fin de chaˆıne pour respecter les cadencements imposés par des normes d’affichage comme celles spécifiées par le VESA [148]. Dans le cadre d’une implémentation des applications de vision, la présence d’un Frame Buffer est impérative pour des opérateurs temporels nécessitant différentes trames d’image `a des indices temporels différents. Nous exposons dans ce chapitre la mise en oeuvre d’un nouveau système mémoire dy namiquement adaptable.

Ce système est intégré `a notre réseau de communication par l’intermédiaire des noeuds maˆıtres, contrˆolant les transactions principales des paquets de données pour ˆetre traités au travers des noeuds esclaves. Après un rappel sur l’organisation traditionnelle des mémoires dans une architecture de calcul pour la vision, nous décrivons notre système de mémorisation basé sur une gestion dynamique de différents emplacements mémoires.

Ces emplacements sont déter minés par des indicateurs que nous imposons pour identifier le positionnement physique d’une trame en mémoire. L’étude de l’intégration du système m´ emoire dédié aux trames, dans notre réseau, nous amène par la suite `a la conception du routeur maˆıtre, capable d’effectuer des requˆetes de lecture et d’écriture de trame d’image. Nous terminons ce chapitre par le prototypage du système mémoire et du routeur maˆıtre, avec une évalua tion en surface et en performance temporelle, dans le cadre d’une implémentation sur un FPGA.

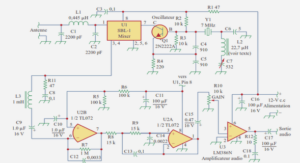

Intégration d’un système mémoire de trames avec le réseau Dans notre réseau de communication, nous avons vu au chapitre 4 que les routeurs maˆ ıtres contrˆolent les transactions principales des paquets de données. Ces routeurs s’échangent ainsi mutuellement des paquets de données correspondant `a différentes images de capteurs différents. Ils représentent `a la fois une source et une destination pour les flux de pixels.

L’adaptation unique du chemin de données n’est cependant pas suffisante pour réaliser efficacement une chaˆıne de traitement composée d’unités de calcul dont les cadencements peuvent ˆetre différents. Ainsi, malgré les possibilités de pipeliner les unités de calcul dans notre réseau, si les bufferisations internes ne suffisent plus pour tenir les cadences im posées, alors les performances en temps d’exécution des calculs s’en trouvent dégradées.

Cette dégradation impacte ainsi la cadence trame en sortie du système. Dans le but de garantir les performances et de permettre l’utilisation d’opérateurs tem porels pour nos applications, nous devons intégrer au réseau une organisation mémoire spécifique permettant de stocker différentes trames image. La mise oeuvre d’une orga nisation mémoire a pour but de réduire les goulots d’étranglement de données dans le réseau et d’assurer la synchronisation des flux de données. Notre réseau, complété avec un système de mémorisation, est proposé en figure 6.1

Le système de mémorisation proposé, est intégré au réseau en le connectant `a tous les routeurs maˆıtres. La mémoire dediée aux trames est alors partagée entre les routeurs maˆ ıtres et ils peuvent ainsi s’échanger des trames sans besoin de les communiquer par le biais du réseau. Cette solution permet ainsi de conserver le maximum de bande passante du réseau pour le traitement des paquets de données par les unités de calcul (PEs) raccordés aux routeurs esclaves.

Nous rappelons que les routeurs maˆ ıtres sont dotés d’interfaces d’entrée et de sortie, pour les flux pixéliques provenant des capteurs et vers les afficheurs. Les routeurs maˆıtres représentent ainsi les interfaces du réseau de communication avec l’extérieur. Nous pouvons remarquer que ces interfaces avec l’extérieur auraient pu ˆetre considérées directement sur le système de mémorisation de trames.

Ce choix impliquerait ainsi une simplification de la conception du routeur maˆıtre. Cependant, cette solution imposerait un chemin de données critique, comme celui présenté en figure 6.2(b), dépendant forcé ment d’accès en mémoire en entrée et en sortie. Ce choix augmenterait ainsi la latence de sortie. Elle ne permettrait donc pas d’établir un flot de données direct entre deux noeuds maˆıtres au travers des routeurs esclaves, comme illustré en figure 6.2(a)