Système de mémorisation dynamiquement adaptable

Intégration d’un système mémoire de trames avec le réseau

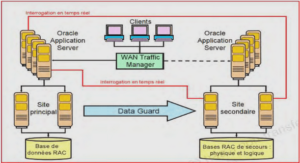

Dans notre réseau de communication, nous avons vu au chapitre 4 que les routeurs maˆıtres contrˆolent les transactions principales des paquets de données. Ces routeurs s’échangent ainsi mutuellement des paquets de données correspondant à différentes images de capteurs différents. Ils représentent à la fois une source et une destination pour les flux de pixels. L’adaptation unique du chemin de données n’est cependant pas suffisante pour réaliser efficacement une chaˆıne de traitement composée d’unités de calcul dont les cadencements peuvent ˆetre différents. Ainsi, malgré les possibilités de pipeliner les unités de calcul dans notre réseau, si les bufferisations internes ne suffisent plus pour tenir les cadences imposées, alors les performances en temps d’exécution des calculs s’en trouvent dégradées. Cette dégradation impacte ainsi la cadence trame en sortie du système. Dans le but de garantir les performances et de permettre l’utilisation d’opérateurs temporels pour nos applications, nous devons intégrer au réseau une organisation mémoire spécifique permettant de stocker différentes trames image. La mise oeuvre d’une organisation mémoire a pour but de réduire les goulots d’étranglement de données dans le réseau et d’assurer la synchronisation des flux de données. Notre réseau, complété avec un système de mémorisation, est proposé en figure 6.1 .Le système de mémorisation proposé, est intégré au réseau en le connectant à tous les routeurs maˆıtres. La mémoire dediée aux trames est alors partagée entre les routeurs maˆıtres et ils peuvent ainsi s’échanger des trames sans besoin de les communiquer par le biais du réseau. Cette solution permet ainsi de conserver le maximum de bande passante du réseau pour le traitement des paquets de données par les unités de calcul (PEs) raccordés aux routeurs esclaves. Nous rappelons que les routeurs maˆıtres sont dotés d’interfaces d’entrée et de sortie, pour les flux pixéliques provenant des capteurs et vers les afficheurs. Les routeurs maˆıtres représentent ainsi les interfaces du réseau de communication avec l’extérieur. Nous pouvons remarquer que ces interfaces avec l’extérieur auraient pu ˆetre considérées directement sur le système de mémorisation de trames. Ce choix impliquerait ainsi une simplification de la conception du routeur maˆıtre. Cependant, cette solution imposerait un chemin de données critique, comme celui présenté en figure 6.2(b), dépendant forcément d’accès en mémoire en entrée et en sortie. Ce choix augmenterait ainsi la latence de sortie. Elle ne permettrait donc pas d’établir un flot de données direct entre deux noeuds maˆıtres au travers des routeurs esclaves, comme illustré en figure 6.2(a)

Hiérarchie mémoire

Nous pouvons décomposer l’architecture d’un noeud maˆıtre en trois parties : une partie contrˆole, une partie mémorisation et une partie réservée à l’adaptation du chemin de données et des accès en mémoire. Comme illustré en figure 6.1, chaque noeud maˆıtre possède un accès en lecture et écriture sur une mémoire partagée de grande capacité permettant de stocker différentes images qui sont véhiculées dans le réseau sous forme de paquets de données. Comme étudié au chapitre 2, dans le domaine de la vision, les unités de calculs manipulent généralement trois types d’entrée : le pixel, la ligne et la trame. Dans le système complet réseau et mémoire que nous avons proposé, nous pouvons identifer deux niveaux de mémoire pour le noeud maˆıtre (Figure 6.3). Le premier niveau est une mémoire locale, à accès aléatoire, dont la capacité permet de stocker plusieurs lignes d’une trame image selon sa résolution. Le second niveau correspond aux mémoires de trames, à accès lignes, qui sont stockées dans le système mémoire partagé. Le contrˆoleur, inclus dans le noeud maˆıtre, effectue des requˆetes de lecture et d’écriture au système de mémorisation de trames. Chaque requˆete est réceptionnée par un serveur de trames central qui se charge de décoder les requˆetes afin de récupérer les informations nécessaires à l’adressage de la mémoire. Suivant ces informations, il adapte le chemin de données et les accès mémoires pour diriger les flux de données entrants et sortants vers le routeur maˆıtre ayant effectué la requˆete. Le décodage et l’adaptation du système mémoire introduisent une latence globale des différents accès qui doit ˆetre minimisée. Afin de masquer les latences d’adaptation d’accès en mémoire partagée mais aussi permettre des accès pixéliques spécifiques, les données trames peuvent ˆetre chargées partiellement par exemple dans les mémoires lignes contenues dans un noeud maˆıtre. Le tableau 6.1 résume les caractéristiques de chaque mémoire (type, maˆıtre, accès)Par rapport aux noeuds maˆıtres, les mémoires lignes sont locales et les mémoires de trames sont globalement partagées. Lorsque plusieurs lignes ont été chargées dans les mémoires locales, elles peuvent ˆetre accédées suivant différents modes (lecture successive, saut de pixels, formes spécifiques) prédéfinis dans les générateurs d’adresses contenus dans le noeud maˆıtre. Ces modes sont utiles dans le cas o`u les unités de calcul n’ont pas de mémoire locale et ne sont ainsi pas capable d’accéder de manière aléatoire sur une ligne de la trame.