SYNTHESE NUMERIQUE ET IMPLEMENTATION D’UN SYSTEME DE QUANTIFICATION PHA DANS UN FPGA

Avec la technologie actuelle, façonnée par la recherche de miniaturisation et de performance toujours plus poussée, la percée sur le marché de l’instrumentation des circuits FPGA se fait remarquer. Ceux-ci se démarquent particulièrement par l’immensité de leur densité d’intégration, qui leurs permet d’exploiter au maximum l’avantage d’une structure de traitement de données exécuté ensemble en parallèle, sur des mémoires statiques, sans : rapidité. Sans oublier le fait que ceux-ci sont programmables, donc plus rapide à développer et présentent plusieurs avantages : de loin moins onéreux et légers, si on compare aux nombres que ceux-ci nécessitent et le poids que ceux-là représentent en utilisant des composants discrets.

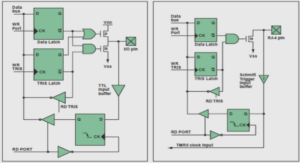

SPARTAN2 de la carte UNIO52 (Jülich)

Dans le premier prototype de développement, le système de spectrométrie d’amplitude (PHA) a été implanté dans un FPGA de référence XC2S150, qui est intégré dans la carte d’acquisition universelle UNIO52. Le système est piloté par un microcontrôleur AN2131Q, basé sur un processeur 8051 amélioré ayant les principales caractéristiques suivantes : – Horloge de fréquence à 24MHz – Cycle d’instruction à 4-périodes – 256 bytes de registres de mémoire interne Le microcontrôleur AN2131Q est un circuit intégré est de la famille des « Cypress Semiconductor EZ-USB » Série 2100, qui intègre les fonctions matérielles et logicielles nécessaires au protocole de communication USB : module d’interface SIE/USB (ou “USB Core”). Figure-4. 21 : Schéma bloc du microcontrôleur AN2131Q Figure-4. 22 : Caractéristiques du microcontrôleur AN2131Q Etant donné les spécifications du microcontrôleur AN2131Q, en particulier la capacité de la mémoire RAM de 8Ko, l’utilisation de la carte est limitée pour une spectrométrie de faible résolution de 1024 canaux. En effet si on veut mesurer jusqu’à 32-bits de données sur chaque canal, on doit allouer 4x8x1024 bits, soit 4Ko de mémoire pour le spectre. Les 4Ko d’espace mémoire restante, seront nécessaires pour le code de programmation. C’est la raison pour laquelle, le projet a été développé pour fonctionner avec un système de détection à NaI(Tl), lequel ne demande qu’une résolution en canaux de 1K. Aucun traitement numérique supplémentaire n’est nécessaire, à part la gestion (lecture et écriture) de registres de mémoires. La configuration du FPGA à partir de langage VHDL est suffisante et a été effectuée (code en Annexe-A1). Les données binaires à 12bits, générées par le convertisseur AD9224 correspondant aux amplitudes des signaux d’impulsions sont transmises à une fréquence de 24MHz au FPGA. Le principe de la détection du pic est décrit dans [11], celui-ci consiste à comparer, la valeur du signal échantillonné en temps réel, par rapport à des seuils de références bien définis, et en adapter l’action à faire selon le résultat du test de comparaison.

SPARTAN3E de la carte EFM01 (Cesys)

Avec l’arrivée sur le marché de la carte d’acquisition universelle EFM01 (de Cesys) en 2013, le système de spectrométrie d’amplitude (PHA) a pu être développé dans un FPGA Spartan-3E de référence XC3S500E, implanté sur la carte. Les données binaires de 14bits, générées par le convertisseur LTC2248 correspondant aux amplitudes des signaux d’impulsions sont transmises à une fréquence de 24MHz au Spartan-3E. La carte d’acquisition est pilotée par un microcontrôleur CY7C68013A, basé sur un processeur 8051 amélioré, comme le modèle AN2131Q précédent, mais présentant des performances encore meilleures. Entre autres, une capacité de 16Ko d’espace mémoire statique (RAM), qui donne plus de possibilité pour une spectrométrie à haute résolution (jusqu’à 4096 canaux).