Les systèmes sur puce (System-on-Chip ou SoC) ont vu leur utilisation largement se répandre durant ces quinze dernières années. Ce phénomène s’explique notamment par leur large adoption dans les systèmes embarqués grand public tels que les tablettes ou les smartphones, et ceci pour plusieurs raisons.

Pour commencer, en les comparant aux systèmes basés sur des CPU qui équipent la plupart des ordinateurs, leur consommation en énergie est faible, tout en délivrant des puissances de calculs élevées. Le fait qu’un ou plusieurs processeurs, puissent partager la même puce en silicium que des mémoires et des périphériques, réduit drastiquement les pertes en énergie autrement dues à la présence de bus externes reliant différents circuits. Cette caractéristique commence d’ailleurs à attirer l’attention d’acteurs d’un domaine où jusqu’ici les SoC étaient très minoritaires et où les problématiques de consommation sont d’importance capitales, il s’agit des supercalculateurs. En effet, soit le Japonais Fujitsu [SICa], soit les constructeurs Bull et Cray [SICb] pour l’Europe, ont annoncé la conception de nouvelles architectures de calculs à hautes performances basées sur des SoC ARM.

Une autre raison qui explique la large adoption des systèmes sur puce, est leur encombrement spatial réduit au regard du nombre de fonctions qu’ils peuvent contenir. Cela concerne entre autres, les protocoles de communication sans-fils (3G/4G, Wifi, Bluetooth, NFC), la gestion l’audio (micro, haut-parleur), de la vidéo (écran, processeur graphique), ou des cartes SIM et cartes mémoires externes. Grâce à l’amélioration des technologies de conception, le nombre et la complexité des fonctions embarquées s’amplifient, tout en minimisant les surfaces qu’occupent les circuits.

Désormais, les architectures capables d’interconnecter les éléments au sein des systèmes sur puce doivent suivre la même évolution en performances. Des bus sont habituellement utilisés dans l’optique de supporter les communications, cependant leur bande-passante se trouve limitée lorsque le nombre d’éléments communicants est excessif. Partant de ce constat, des personnes ont cherché des architectures, dit « scalable », c’est-à-dire, pouvant supporter une augmentation des besoins en bande-passante, sans engendrer une dégradation de leurs autres performances. Pour trouver des solutions, ces personnes se sont tournées vers un domaine où ces problématiques se sont déjà posées, il s’agit des réseaux informatiques. D’où l’idée de porter des architectures se reposant sur des réseaux de routeur dans les circuits électroniques [BEN02]. Ce type de système d’interconnexions est appelé « réseau sur puce » (Network-onChip ou NoC). Les systèmes sur puce sont majoritairement intégrés dans des circuits ASIC (Application Specific Integrated Circuit), non reprogrammables et ayant des coûts initiaux de conception et de production très élevés. Ce n’est qu’en produisant des volumes de circuits conséquents que le montant de l’étape de conception devient négligeable par rapport au coût total, et que le prix unitaire d’un circuit s’effondre. Les phases de tests et de validations sont très importantes puisque les erreurs de conception ne peuvent pas être corrigées une fois le circuit fabriqué. Les circuits FPGA (Field Programmable Gate Array) sont notamment utilisés lors du prototypage des circuits ASIC, grâce à la possibilité qu’ils offrent d’être reprogrammés. Cependant, leur utilisation ne se cantonne pas qu’à cette fonction, puisqu’ils peuvent tout aussi bien être utilisés dans des produits finis, particulièrement dans des secteurs comme la défense, l’avionique, l’aérospatial ou le médical. Les systèmes implémentés sur FPGA sont appelés systèmes sur puce reprogrammables.

Les architectures matérielles des ASIC et des FPGA sont très différentes. Les circuits ASIC sont pour ainsi dire, « taillés sur mesure » pour l’application qu’ils fournissent. Pour les FPGA, ce n’est pas le cas puisque les constructeurs ne peuvent pas savoir par avance, quels types d’applications vont être implémentés dans le circuit. La quantité et la disposition des ressources logiques à l’intérieur de la puce sont ainsi prévues pour une certaine polyvalence. Comme les systèmes d’interconnexions sont tributaires des architectures des circuits sur lesquels ils sont utilisés, et que les recherches concernant les réseaux sur puce se sont surtout intéressées aux implémentations sur ASIC, sur plateforme FPGA il faut chercher à tirer parti au mieux des ressources disponibles en adaptant le système d’interconnexions.

Un aspect à ne surtout pas négliger lors de la conception des systèmes numériques modernes est la sécurité. Les SoC par nature, fournissent un niveau certain niveau de protection contre les attaques matérielles, puisque quasiment tous les composants du système sont intégrés dans une seule puce de silicium. Cela empêche un attaquant de positionner une sonde au niveau d’un bus externe dans le but d’espionner les données qui transitent dessus, voire de les modifier. Cependant, la sécurisation des systèmes numériques est un très vaste sujet et de nombreuses failles sont potentiellement présentes au niveau matériel ou logiciel. Par exemple, lors de l’exécution du système d’exploitation, des environnements cloisonnés et sécurisés doivent être fournis aux applications pour éviter qu’un processus malicieux (virus, ver, cheval de troie…) puisse accéder au contenu privé ou sensible, manipulé par une autre application.

Au niveau matériel, il est théoriquement possible qu’un des acteurs ayant un rôle dans le flot de conception puisse ajouter délibérément ou par négligence, une faille ou une porte dérobée au circuit [SKO12]. Lorsque cette action est délibérée, on dit qu’il s’agit d’un cheval de Troie matériel (Hardware Trojan) [TEH10]. Les délais de mise sur le marché des produits tendent à être les plus courts possibles, et dans le but de les minimiser, la réutilisation d’un certain nombre de fonctions d’un produit à l’autre est quasiment obligatoire. Ces fonctions, pouvant être aussi bien matérielles que logicielles, sont appelées cœur de propriété intellectuelle ou plus couramment IP (Intellectual Property). Les IP se vendent et s’achètent entre tiers, elles sont assemblées et intégrées pour former des systèmes complexes. Il n’est pas exclu qu’une de ces IP contiennent une faille ou un processus malicieux, menant à des attaques pouvant bloquer le système ou bien divulguer des données qu’il manipule. Dans des domaines comme la défense, où les systèmes cryptographiques sont très utilisés, la confidentialité des données est capitale.

Sur ce point, l’ajout de mécanismes de sécurité aux systèmes d’interconnexions peut être une aubaine pour la sécurisation matérielle et logicielle du système sur puce. En effet, la position centrale du réseau gérant les communications, peut lui permettre de contrôler les échanges entre les différents cœurs et d’identifier d’éventuelles tentatives d’intrusion. Des contremesures peuvent ensuite être appliquées pour empêcher qu’une n’attaque atteigne ses objectifs.

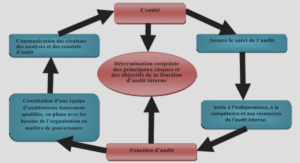

Ce travail de thèse est effectué dans le cadre d’une convention industrielle de formation par la recherche (CIFRE). Cette CIFRE est le fruit d’un partenariat entre le laboratoire d’informatique, de robotique et de microélectronique de Montpellier (le LIRMM) et le service Trustway appartenant à la société Bull-Atos.

Le service Trustway a pour rôle le développement de produits de sécurité, tels que le disque dur sécurisé Globull ainsi qu’une gamme de modules de sécurité matériels (HSM pour Hardware Security Module). Les HSM sont des ressources matérielles fournissant un ensemble de services cryptographiques tels que du chiffrement symétrique, asymétrique, des signatures, et des algorithmes de hachage. Ces modules sont évalués par des cabinets indépendants afin d’obtenir des certifications (telles que la FIPS-140 ou les Critères Communs EAL+) attestant que leur conception respecte certaines règles de sécurité. Ces règles sont définies par des agences gouvernementales tels que l’ANSSI pour la France ou NIST pour les Etats Unis [ANS], [NIS].

L’utilisation de plateformes matérielles telles que les HSM, est largement préconisée pour la réalisation de produits électroniques, où la sécurité est une des préoccupations premières, notamment en ce qui concerne la génération et le stockage des clés cryptographiques ([TPM], [TCG11] et [FIS11]). Pour concevoir ses HSM, la société Bull emploie des circuits FPGA. Ils ont pour principale charge, la gestion des clés cryptographique et l’exécution des différents algorithmes de chiffrement et de hachage. Ce type de circuit est adapté à la fabrication de quantités faibles ou moyennes de produits, contrairement à une utilisation d’ASIC pour effectuer les mêmes tâches. Ces derniers ont des coûts de conception et de validation très élevés, et qui ne peuvent être rentabilisés que par d’importants volumes de production. En outre, l’avantage des FPGA en tant que plateformes reconfigurables, est de pouvoir supporter des mises à jour de leur programme via des patchs correctifs, résolvant des problèmes fonctionnels ou des failles de sécurité.

On peut s’interroger sur la possibilité qu’une plateforme logicielle supportée par un CPU, remplace les circuits FPGA pour l’exécution des calculs cryptographiques. Cependant, pour beaucoup de ces algorithmes, une implémentation matérielle permet d’obtenir de bien meilleures performances. Bien que la fréquence d’horloge puisse être 10 fois moins élevée sur circuit reprogrammable que sur CPU, la parallélisation de certains calculs sur FPGA, augmente drastiquement les débits de certains algorithmes de cryptographie.

Les systèmes sur puce conçus par le service Trustway comportent de plus en plus de cœurs, par conséquent, les systèmes d’interconnexions jusqu’ici utilisés sont confrontés à un problème de manque évolutivité. D’où l’intérêt que porte ce département aux systèmes sur puce optimisés pour circuits FPGA, dont notamment les réseaux sur puce. La sécurité matérielle et logicielle des produits que le service conçoit est également capitale, il est primordial de s’assurer que l’emploi d’un réseau sur puce n’ouvre pas de nouvelles vulnérabilités. Pour pallier ce risque, l’étude des mécanismes de sécurité pouvant être ajoutés au système d’interconnexions est nécessaire.

Les systèmes sur puce sont réalisés grâce à un assemblage d’IP, dans lequel chacune joue un rôle bien particulier. Généralement, on peut classer les IP dans deux catégories. La première catégorie d’IP qui initie les requêtes est appelée maître. La seconde qui reçoit ces requêtes est appelée esclave. Il peut s’agir de processeurs exécutant du code logiciel, des accélérateurs cryptographiques, des interfaces de communications, des mémoires, des unités de traitement audio ou vidéo, ainsi que divers périphériques. Pour que le système sur puce fonctionne avec des performances suffisantes, toutes ces IP doivent pouvoir échanger des informations à des débits minimaux, et des latences maximales.

Pour remplir cette fonction, de nombreux types de systèmes de communications sont envisageables. Cependant, ils sont tributaires de beaucoup de caractéristiques, comme le nombre de nœuds à faire communiquer, la largeur des liens, la taille et la fréquence d’émission des messages, le débit, la latence, et la plateforme matérielle ciblée.

Bus

Le bus est sûrement l’architecture la plus commune. tous les nœuds sont connectés au même medium, composé au minimum, d’un bus de contrôle ou de requête, d’un bus d’adresse et d’un bus de données. Les esclaves utilisent le bus d’acquittement pour répondre aux requêtes provenant des maîtres. Lorsqu’un nœud émet un message, il est diffusé à tous les autres, mais auparavant l’arbitre central régissant les accès devra avoir autorisé la transmission.

La principale limitation de ce type d’architecture réside dans la bande-passante qui est partagée entre tous les nœuds émetteurs. Comme il n’y a qu’un seul nœud qui peut accéder au bus à la fois, lorsque le nombre de nœuds est trop important, la bande-passante n’est plus suffisante pour pouvoir satisfaire les performances du système. Il existe de nombreuses de variations et de spécifications différentes de bus, certaines offrant la possibilité d’effectuer des requêtes en « burst », ciblant plusieurs mots d’un registre mémoire, ou bien encore intégrant des mécanismes de gestion d’erreur, avec des réémissions de messages en cas de détection d‘une faute intervenant lors de la transmission. Pour donner quelques exemples de bus très utilisés, on peut citer le bus AMBA – AXI proposé par ARM [XIL15], le bus CoreConnect d’IBM [IBM99] ou encore le bus open source Wishbone [WIS10].

Pour pallier le problème de limitation de bande-passante, des architectures basées sur des hiérarchies de bus ont été proposées [KHA16], il s’agit de plusieurs bus connectés par des ponts. Cependant elles se révèlent très vite limitées, puisque lorsqu’une IP souhaite communiquer avec une IP connectée à un autre bus, elle va devoir monopoliser le bus pour accéder au pont, puis monopoliser tous les bus intermédiaires jusqu’à atteindre l’IP destinataire.

Crossbar

Ce type d’architecture a l’avantage de supporter plusieurs connexions en parallèle, dans la mesure où les IP initiatrices et réceptrices ne sont pas déjà impliquées dans un échange. d’adresse et de données ont été simplifiés en simples flèches dans un souci de lisibilité.

Le problème d’évolutivité rencontré lors de l’augmentation du nombre de nœuds se retrouve aussi dans les architectures en crossbar. Contrairement au bus, la limitation n’est pas causée par la bande-passante, car il y a plusieurs médias partagés entre toutes les IP. Par contre, la complexité et la surface des multiplexeurs et des démultiplexeurs augmentent de façon très importante avec l’accroissement du nombre d’entrées et de sorties.

Système d’interconnexions propriétaires

Comme nous avons pour objectif d’implémenter le système d’interconnexions sur FPGA, nous avons étudié les options disponibles dans les outils de conception des vendeurs de ces circuits. Il s’agit par exemple, du bus AXI4 pour Xilinx [XIL15], ou Qsys pour Altera/Intel FPGA [QSY]. Ces solutions sont potentiellement très performantes car elles sont développées par les entreprises qui réalisent les architectures matérielles des FPGA, et donc qui peuvent exploiter leur connaissance totale du matériel pour optimiser les systèmes d’interconnexions, notamment à travers les algorithmes de placements-routages.

Cependant, la principale limitation de ces systèmes propriétaires réside dans leur opacité. En effet, comme les codes sources de ces architectures sont secrets et chiffrés, il est donc impossible d’effectuer des recherches sur la présence éventuelle de failles de sécurité. Cette opacité est sans doute premièrement motivée par la protection du secret industriel, cependant, elle rentre souvent en contradiction avec les objectifs relatifs à la sécurit .

Introduction générale |