Télécharger le fichier original (Mémoire de fin d’études)

Le modèle du composant chargé CDM

Le modèle du composant chargé ou Charged Device Model (CDM) reproduit la décharge d’un composant ou d’un circuit intégré assemblé qui s’est chargé. Un exemple typique de décharge CDM est un composant glissant de son tube de transport et atterrissant sur une surface conductrice. Les frottements des broches et du boitier avec le tube permettent de stocker des charges qui sont par la suite évacuées à travers une broche. Le phénomène CDM a donc lieu lorsqu’un contact métal à métal est établi suite à un transfert du composant dans une zone à champ électrique, ou sa charge par le phénomène de triboélectricité.

La quantité de charges stockées demeure très variable d’un composant à un autre et la forme de l’impulsion de l’ESD dépendra des conditions d’intégration en boîtier. Dès lors, il devient très difficile de simuler expérimentalement ce modèle. Néanmoins, plusieurs simulateurs de décharges ont été développés afin de reproduire la décharge avec des circuits à base d’une résistance. La différence fondamentale de ces simulateurs réside dans le moyen de charge du composant.

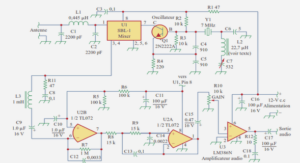

La Figure 5 montre le circuit électrique équivalent simulant la décharge CDM. Nous distinguons une résistance de 10 Ω mise en série avec une bobine de 0,5 nH. Le circuit (a) correspond au mode de charge directe du composant avec une connexion des broches, tandis que le schéma électrique simplifié (b) est représentatif d’une décharge de type induite. L’impulsion CDM directe est plus reproductible en pratique. Elle possède une intensité de courant de décharge très dépendante de la valeur de la capacité parasite [9].

Quelque le mode de décharge, l’impulsion CDM dans un court-circuit (Figure 6) se caractérise par un temps de montée très bref compris entre 100 ps et 500 ps et une durée d’impulsion d’environ 5 ns.

Le modèle HBM selon la norme IEC ou modèle du « pistolet »

Pendant plus de trois décennies, de nombreuses précautions ont été mises en place par les industriels face aux décharges électrostatiques sur les composants discrets en plus du système électronique entier [10]. Historiquement, le modèle accepté par les fabricants et les clients pour définir les menaces ESD était l’HBM. Récemment, un nouveau modèle a émergé. La norme IEC 61000-4-2 devenant le standard de l’industrie de la microélectronique pour simuler l’ESD, les clients exigent désormais que cette norme soit appliquée aux systèmes et parfois même aux circuits intégrés. Ainsi, le développement de ce modèle aussi appelé « pistolet » a permis d’évaluer l’immunité des produits dans leur application finale face aux diverses contraintes environnementales. En effet, le modèle du « pistolet » se définit comme étant la simulation de la décharge d’une personne, à travers un système électrique ou électronique, tenant du bout des doigts un objet métallique [11]. L’illustration du mode de décharge est donnée sur la Figure 7 pour une personne se déchargeant sur un système électronique à travers un tournevis.

Modèle IEC 61000-4-2

En 1995, la Commission Electrotechnique Internationale (CEI) ou International Electrotechnical Community (IEC) publie un nouveau modèle HBM standard plus sévère connu sous le nom d’IEC 801-2 [12]. Cette spécification est destinée à définir les performances exigées de tous les composants électroniques dans une série de conditions d’interférences électromagnétiques. En effet, la norme IEC 801-2 résulte d’un marché commun Européen et d’une forte exigence à la fiabilité des systèmes électroniques. Ainsi, elle connaît successivement deux numérotations différentes par la CEI dans le but de regrouper toutes les spécifications électroniques au sein de la communauté Européenne. Jusqu’en 1997, la norme est connue sous le nom IEC 1000-4-2 avant de porter la numérotation actuelle : IEC 61000-4-2 [13].

Les modifications dans l’appellation ont été effectuées sans changement de la description du modèle. Elle a toujours consisté en une représentation schématique (Figure 8) d’un condensateur de capacité 150 pF se déchargeant à travers une résistance de 330 Ω. Dans un premier temps, l’interrupteur est fermé sur le générateur haute tension afin de charger le condensateur. Ensuite, un basculement de l’interrupteur en position ouverte initie la décharge du condensateur à travers la résistance de 330 Ω et l’bobine pour atteindre le composant sous test. La forme d’onde en courant vue par une résistance de 2 Ω substituant le composant sous test est caractéristique de la norme IEC 61000-4-2.

Deux modes d’application de la décharge existent: au contact ou à l’air. Idéalement, la méthode d’essai à utiliser serait la décharge au contact car dans l’air la reproductibilité de la mesure est mauvaise [14]. Ainsi, les décharges dans l’air doivent donc être utilisées uniquement lorsque les décharges au contact ne sont pas applicables.

Figure 8: Schéma électrique simplifié de génération de décharges selon la norme IEC 61000-4-2

La forme d’onde du pistolet

Comme son nom l’indique, le modèle HBM de la norme IEC 61000-4-2 s’apparente donc au modèle HBM pour les circuits intégrés avec comme principale différence une décharge véhiculée au travers d’objets métalliques tels que des clés ou des tournevis. Par conséquent, l’HBM de la norme IEC se distingue du modèle HBM par le temps de montée et l’intensité du courant de décharge [15]. Ainsi, l’onde typique IEC 61000-4-2 est formée de deux pics dont le premier caractérise la décharge du métal de faible résistance et le second pic correspond à la décharge du corps humain. Cependant, l’intensité du premier pic de courant est très importante comparée aux modèles HBM, MM et CDM. L’impulsion décrite par la norme IEC 61000-4-2 se caractérise par une onde en courant présentant un temps de montée inférieur à 1 ns et une durée d’impulsion d’environ 120 ns (Figure 9). Cette forme d’onde combine en quelque sorte le temps de montée de la décharge CDM et la durée d’impulsion de l’onde HBM.

Figure 9: Forme d’onde de la norme IEC 61000-4-2 délivrée par un simulateur de décharge de type « pistolet ».

Trois paramètres temporels sont essentiels pour la définition et la standardisation de la forme d’onde en courant générée par le « pistolet » selon la norme IEC 61000-4-2. Ainsi, aux pics, à 30 ns et à 60 ns, les intensités de courant doivent atteindre les valeurs résumées dans le tableau 1 pour des tensions de charge données. Le très court temps de montée tR doit être compris entre 0,7 ns et 1 ns et correspond à la différence temporelle entre 10% et 90% de l’intensité Ipic du premier pic de l’onde. Dès lors, les simulateurs de décharge doivent tous délivrer une forme d’onde en courant répondant aux caractéristiques expérimentales résumées dans le Tableau 1.

Les simulateurs de décharge

Aujourd’hui, les fabricants de testeurs proposent différents simulateurs de décharge satisfaisant la norme IEC 61000-4-2. La problématique de ces simulateurs réside dans le fait qu’ils peuvent donner des résultats différents sur l’évaluation des niveaux d’immunité tout en répondant pourtant aux spécifications de la norme IEC 61000-4-2 [16,17,18]. Autrement dit, des testeurs provenant de différents fabricants vont donner des résultats différents pour un même composant. Finalement, la forme d’onde non fiable mène à des résultats de mesure de robustesse non reproductibles [19].

La complexité de la mesure rend les spécifications établies dans le standard incomplètes. En effet, les courants de décharge sont très dépendants du composant testé [20]. Ainsi, P. Leutchmann décrit la possible origine de la faille de la norme comme résidant dans l’absence de renseignements sur les champs électriques et magnétiques aux points d’injection de la décharge [21]. L’émission des radiations électromagnétiques autour de la pointe de décharge a aussi contribué au développement d’impulsions IEC à partir d’un système de décharge à ligne de transmission.

En effet, le simulateur de décharges à ligne de transmission offre une qualité d’impulsions significativement meilleure. La suppression des rayonnements électromagnétiques à proximité du circuit testé s’effectue lorsque toutes les composantes du système sont dotées d’une impédance 50 Ω. Deux types de simulateurs de décharges existent donc aujourd’hui : le testeur muni d’une ligne à transmission reproduisant la forme d’onde de la norme IEC 61000-4-2, et d’autre part le « pistolet » qui, par contre, est un dispositif dans le respect de la norme IEC61000-4-2 exigeant une impédance de 330 Ω et un condensateur série de 150 pF.

Le modèle HMM

En plus de la fiabilité du système, de nombreux fabricants de circuits intégrés rencontrent aussi des difficultés à garantir la fiabilité de leurs produits vis-à-vis des ESD lorsqu’ils sont intégrés dans le système final du client [22]. En effet, la norme IEC 61000-4-2 est uniquement conçue pour garantir l’immunité des systèmes électroniques [23]. Cependant, son application n’est pas du tout prévue sur un circuit intégré ou un composant électronique discret malgré des demandes croissantes provenant des concepteurs de systèmes [24]. Ainsi, dans le but d’étendre le domaine d’application de l’IEC aux circuits intégrés et aux composants discrets afin de garantir la fiabilité de la mesure, l’Association ESD (ESDA), fondée en 1982, propose une nouvelle méthode de mesure : l’HMM. Les formes d’onde produites sur un composant sont donc dénommées HMM pour Human Metal Model afin de les distinguer des décharges appliquées sur un système [25]. Cette méthode de caractérisation faisant toujours référence à la norme IEC 61000-4-2, la flexibilité de la norme HMM présente par conséquent l’avantage de garantir des immunités ESD fiables au niveau du composant et du circuit intégré.

L’HMM reproduit la forme d’onde ESD de la norme IEC 61000-4-2 [26] pour ainsi toujours simuler la décharge d’une personne debout à travers un objet métallique [27]. Actuellement, la source de ligne de transmission 50 Ω est identifiée comme pouvant reproduire la même forme d’onde de courant pour une tension IEC équivalente au « pistolet » [28]. La Figure 10 représente, en guise d’illustration, la décharge dans un court-circuit de 10 kV de tension de charge équivalente à un « pistolet » en utilisant un système à ligne de transmission 50 Ω. Ce système appelé 4702 IEC50, a été développé par Barth Electronics afin de délivrer des impulsions avec un courant maximum de 100 A soit près de 30kV en équivalence IEC. Toutefois, il faut remarquer que la forme d’onde est en parfaite adéquation avec celle décrite par la norme IEC 61000-4-2. Cependant, aucun détail du dispositif électrique permettant de générer cette forme d’onde n’est renseigné par le fabricant sous couvert de la confidentialité.

Ce modèle HMM autorise désormais l’évaluation de l’immunité ESD au niveau du composant et du circuit intégré. Sa standardisation est initiée depuis quelques années par l’ESDA. Cependant, elle reste aujourd’hui très controversée puisque la variation d’impédance entre le banc du « pistolet » et l’HMM est susceptible d’induire des perturbations dans les circuits empruntés dans le système électronique durant la décharge. Par conséquent, l’utilisation de l’HMM est déconseillée au niveau du système. L’HMM ne pourra en aucun cas garantir une immunité en remplacement du « pistolet ».

Conclusion

Dans le milieu industriel de l’électronique, des confusions sont faîtes dans l’utilisation du terme HBM. Pour des circuits intégrés, l’immunité ESD en HBM décrit une décharge provenant du bout du doigt d’une personne en faisant référence à une norme JEDEC très familière. Le terme HBM est parfois exploité pour décrire la décharge d’une personne tenant un objet métallique sur un système, c’est-à-dire le modèle du « pistolet » de la norme IEC 61000-4-2. Afin de distinguer la caractérisation HBM traditionnelle au niveau du composant de celle utilisant la forme d’onde IEC 61000-4-2, l’ESDA a adopté le nom de modèle HMM pour cette dernière. Alors que le modèle du « pistolet » et le modèle HMM exploitent la même impulsion de courant, elles sont toutefois appliquées sur des niveaux différents pouvant aboutir à des niveaux d’immunité différents.

La protection ESD dans le circuit intégré (CI) : exigences industrielles

La notion de protection ESD n’a un sens uniquement si l’entité protégée est définie. L’intérêt de ce paragraphe est de, finalement, décrire tout d’abord le circuit intégré (CI) en relatant son évolution de sa conception à son développement. Les motivations qui mènent à l’intégration d’une protection dans un circuit intégré seront ensuite décrites avant de montrer les conditions requises pour assurer la protection contre les ESD.

Le circuit intégré sur silicium IPADTM

Un circuit intégré est un circuit électrique complexe constitué de plusieurs composants distincts tous compris dans un même assemblage monolithique. Les premières recherches effectuées sur cette technologie remontent à la fin des années 1950. L’objectif était de réduire la taille des systèmes électroniques afin d’inclure une plus grande quantité de fonctions électroniques complexes dans un espace limité. Les différentes approches proposées incluaient des techniques d’assemblage de composants individuels, des structures à film mince et des semi-conducteurs intégrant des circuits. Dans l’évolution de la microélectronique, ces trois approches ont été développées pour finir par être combinées dans une seule et même technologie. Ainsi, cette innovation a progressivement donné naissance aux circuits intégrés dans l’industrie du semi-conducteur.

Dans cette optique, la société STMicroelectronics a récemment proposé des composants actifs et passifs intégrés aussi appelés Integrated Passive and Active Devices (IPADTM). La stratégie visée est de combiner des résistances, condensateurs, bobines, des diodes de protection ESD ainsi que de multiples autres fonctions dans un seul et même boîtier miniature. Cette alternative a permis de répondre aux besoins pressants du marché. En effet, pour des applications telles que : la téléphonie mobile, les ordinateurs, les appareils de consommation et les équipements médicaux, de hautes performances sont très souvent exigées dans un format réduit. La technologie d’intégration de composants passifs et actifs se présentait comme étant la solution idéale en offrant un gain en occupation surfacique et en réduction des coûts. Dès lors, les circuits électroniques ne sont plus constitués d’un simple assemblage de composants discrets mais d’un ensemble de composants reposant sur un même substrat appelé circuit intégré.

Problématique ESD sur Circuits Intégrés

Vers la fin des années 1970, les décharges électrostatiques deviennent problématiques dans l’industrie de la microélectronique. De plus faibles robustesses ESD ont généré des défaillances et des pertes industrielles du fait de la réduction de la taille des technologies. La baisse des dimensions s’est donc accompagnée d’une hausse de la sensibilité des produits [29].

Entre les années 1980 et 1990, les concepteurs de composants électroniques parviennent à réaliser de meilleures protections ESD rendant ainsi les composants moins sensibles. Ce développement a connu un succès en procédant à une identification des paramètres technologiques clés permettant d’accroître la robustesse. En effet, suite à des études approfondies du comportement des composants de protection lors d’une décharge, les dessins de structures et les processus de fabrication ont été modifiées afin de rendre les structures plus robustes.

Plus tard, dans les années 1990, l’exigence grandissante de performances avec l’accroissement de la densité d’intégration de circuits pose problème pour les circuits de protection ESD traditionnels. L’immunité des systèmes vis-à-vis des ESD commence donc à décroître avec la miniaturisation. La situation empire avec l’apparition en production des circuits intégrés de très faibles dimensions. Ainsi, les circuits intégrés sont donc devenus de plus en plus fragiles aux ESD entre 2005 et aujourd’hui. Les décharges électrostatiques sont actuellement à l’origine de nombreux dysfonctionnements des systèmes électroniques et circuits intégrés avec des retours clients dus aux ESD. La nécessité de protéger les circuits intégrés des décharges électrostatiques est alors devenue un des intérêts et une des difficultés majeures des concepteurs de circuits microélectroniques.

Conception de la protection ESD pour un circuit intégré

Différentes stratégies de protection sont adoptées pour protéger le système des agressions extérieures. En effet, de fortes précautions sont mises en place vis-à-vis des décharges d’origine humaine ou structurales durant toutes les étapes de fabrication. Tout d’abord, le port de bracelets, de chaussures ainsi que l’utilisation de chaises antistatiques permet de s’affranchir de la majeure partie des ESD de type HBM. De la finalisation du produit et à sa commercialisation, les risques sont de nouveau présents. De ce fait, des composants de protection sont intégrés en entrée et sortie des circuits pour éviter tout risque de destruction durant le bon fonctionnement du système. Ces composants de protection doivent satisfaire quatre grandes caractéristiques que sont la robustesse, l’efficacité, la rapidité et la transparence.

La robustesse du composant de protection permet d’évacuer tout le courant de décharge sans qu’il ne se dégrade lui-même. A cet effet, la protection ESD doit pouvoir laisser passer de très forts courants pendant toute la durée de l’impulsion.

L’efficacité du composant de protection relève de sa capacité à limiter la tension pour éviter tout dommage du circuit interne à protéger. Idéalement, pour assurer une bonne efficacité, la résistance de la protection doit rester faible au cours d’une décharge et être accompagnée d’un bon contact thermique avec le substrat.

La rapidité réside dans son déclenchement avant toute partie du circuit lors d’une ESD. La dernière caractéristique consiste en la transparence dans le circuit. En effet, la protection ne doit pas interférer avec les autres fonctionnalités du circuit. Il sera recherché pour cela une protection avec une très faible capacité parasite.

Ainsi, la recherche d’une protection adaptée réside en une quête de la stratégie prévoyant des chemins préférentiels aux courants de décharges ESD susceptibles de traverser le circuit. Les principaux composants utilisés et satisfaisant ces critères sont entre autres des diodes, des transistors bipolaires auto-polarisés et des thyristors.

Pour protéger le circuit IPADTM contre les ESD, une diode de protection est rajoutée à toutes les entrées du circuit intégré. Généralement, la protection est mise en série avec le condensateur de manière à obtenir une protection plus efficace. Ainsi, la diode que nous étudierons dans le chapitre suivant doit être connectée au condensateur par deux pistes métalliques reliant chacune des électrodes.

Intérêt de l’étude de la fiabilité des circuits intégrés

Dans le milieu de la microélectronique surgissent actuellement des applications intégrant de multiples fonctions, souvent très portatives, grâce à des circuits électroniques miniaturisés. Ainsi, les problèmes liés à la fragilité des systèmes dans l’environnement extérieur s’accentuent. Le côtoiement de l’électronique mobile telle que la téléphonie avec l’agressivité du milieu extérieur a conduit à la mise en place de sévères conditions de fiabilité particulièrement sur les circuits intégrés. L’objectif du fondeur électronique et de ses clients est de garantir une durée de vie du produit acceptable vis-à-vis des ESD pour l’électronique nomade.

Typiquement pour les circuits intégrés IPADs, la spécification client exigeait une robustesse ESD de 15 kV pour des ESD de la norme IEC 61000-4-2. Depuis, cette spécification requiert non seulement 15 kV de robustesse mais réclame aussi la conservation de toutes les fonctionnalités du circuit suite à la répétition de 1000 décharges de 15 kV sur le circuit intégré [30]. Expérimentalement, il s’est avéré qu’un grand nombre de circuits intégrés ainsi que leurs protections ESD discrètes qui répondaient à une robustesse nettement supérieure à la tension de charge de 15 kV ne garantissaient pas forcément la tenue aux décharges répétitives [31]. La fiabilité ESD des composants de protection et circuits intégrés ne doit donc plus être garantie par la simple évaluation du niveau d’immunité.

C’est dans ce contexte que s’inscrivent les travaux menés dans ce manuscrit. Le but est de déterminer les causes de la défaillance en ESD répétitives afin de délivrer des composants fiables lorsque le produit se retrouvera dans les mains du consommateur. Pour mener à bien cette mission, une compréhension des mécanismes de dégradation constitue la voie permettant d’atteindre les axes d’amélioration pour atteindre les performances exigées par le client. Ainsi, à travers des caractérisations physiques et électriques successives, nous pourrons déterminer le paramètre de conception ou du processus de fabrication à l’origine des dégradations en ESD répétitives.

Conclusion

La fragilité des circuits intégrés a été discutée dans ce paragraphe avec l’évolution technologique. Tendre vers des structures miniaturisées s’accompagne de difficultés à garantir un niveau de fiabilité surtout lorsque l’utilisation du produit électronique est contraint à un environnement très agressif. La norme IEC 61000-4-2 initialement destinée à qualifier l’immunité électromagnétique des systèmes vis-à-vis des ESD voit alors son application de plus en plus demandée sur les composants. Cette norme reproduit les événements quotidiens des utilisateurs face à leur appareil électronique. La compréhension des mécanismes de défaillance permettra ainsi, de répondre aux exigences industrielles. Cette satisfaction consiste d’une part en une amélioration de la robustesse et de l’endurance du composant de protection et d’autre part en une garantie de la même fiabilité suite à son intégration dans le circuit IPADTM. Nous remarquerons que la fiabilité est aussi bien influencée par le processus de fabrication que le dessin des structures électroniques [32]. Le but est de proposer, ici, des circuits intégrés avec de meilleures performances ESD en mettant en évidence tout paramètre susceptible d’influencer le comportement électrique de la structure durant l’ESD.

Analyse physique des défaillances ESD

Une décharge électrostatique est caractérisée par un fort courant. C’est un événement d’une très courte durée. Les décharges électrostatiques mènent à des dysfonctionnements des circuits microélectroniques en induisant des défaillances physiques à des endroits plus ou moins localisés du circuit intégré [33].

Figure 11 : a) Dégradation d’un oxyde et des couches métalliques après un stress ESD sur un condensateur TaON [34] b) Dégradation du semi-conducteur après une décharge de type EOS/ESD [35]

La dégradation ESD affecte les fonctionnalités du circuit intégré en engendrant des défaillances dans les diélectriques, les métallisations [36,37] ou les semi-conducteurs [38,39,40] comme le montre le cliché de la Figure 11. L’accès aux renseignements concernant les étapes de fabrication technologique et de dessin des structures pourrait faciliter la compréhension des phénomènes physiques sous-jacents lors une décharge [41]. Dans une étude des mécanismes de défaillance causés par une ou plusieurs décharges électrostatiques, nous recherchons à décrire un scénario de l’évolution physique de la structure. Cette description part de la génération du défaut jusqu’à la défaillance. La complémentarité des techniques de caractérisation physique dites non destructives et destructives est exploitée. En évoluant idéalement dans le sens de la destruction de la structure, les analyses commencent par les méthodologies non destructives pour ne pas soustraire des éléments de compréhension de l’apparition de la défaillance. Cette procédure permet d’établir une analyse constructive de génération de la défaillance. Par la suite, nous avons mis en œuvre des techniques de caractérisation développées pour l’analyse de défaillance afin d’identifier les paramètres de dessin ou de fabrication influençant la sensibilité de la structure de protection vis-à-vis des ESD.

Dans ce paragraphe, nous établirons un descriptif des différentes techniques de caractérisation exploitées ainsi que leur caractère complémentaire. L’intérêt portera tout d’abord sur la localisation de la défaillance. Ensuite, nous traiterons le besoin d’analyse approfondie en vue d’une identification du défaut ESD. Cependant, l’étude du défaut ne saurait débuter sans une préalable définition du défaut qui se distingue de la défaillance.

Table des matières

Introduction générale

Chapitre I : Protection des circuits intégrés vis-à-vis des décharges électrostatiques (ESD)

I. Introduction

II. Les décharges électrostatiques

II.1 Le modèle humain HBM

II.2 Le modèle de la décharge d’une machine MM

II.3 Le modèle du composant chargé CDM

II.4 Le modèle HBM selon la norme IEC ou modèle du « pistolet »

II.4.1 Modèle IEC 61000-4-2

II.4.2 La forme d’onde du pistolet

II.4.3 Les simulateurs de décharge

II.4.4 Le modèle HMM

II.5 Conclusion

III. La protection ESD dans le circuit intégré (CI) : exigences industrielles

III.1 Le circuit intégré sur silicium IPADTM

III.2 Problématique ESD sur Circuits Intégrés

III.3 Conception de la protection ESD pour un circuit intégré

III.4 Intérêt de l’étude de la fiabilité des circuits intégrés

III.5 Conclusion

IV. Analyse physique des défaillances ESD

IV.1 Le défaut et la défaillance

IV.2 Localisation de la défaillance

IV.2.1 La Microscopie Electronique à Balaye

IV.2.2 L’EMMI

IV.2.3 L’OBIRCh

IV.3 Caractérisation physique approfondie

IV.3.1 Le FIB

IV.3.2 La Révélation Chimique

IV.4 Conclusion

V. Conclusion.

Références Bibliographiques

Chapitre II : Etude de la diode de protection ESD

I. Introduction.

II. La diode bidirectionnelle

II.1 Architecture de la structure

II.2 Influence des paramètres géométriques

II.2.1 Variation de la distance entre jonctions N+

II.2.2 Géométrie de la diode

II.3 Conclusion

III. Fonctionnement dans un régime de « fort courant »

III.1 L’outil de caractérisation TLP : Dispositif électrique

III.2 Intérêt de la caractérisation à ligne de transmission

III.3 Comportement de la diode : Principe de mesure d’une caractéristique TLP

III.4 Caractérisation TLP des diodes bidirectionnelles

IV. Fonctionnement électrique statique

IV.1 Etude théorique de la caractéristique statique

IV.1.1 Polarisation de la jonction

IV.1.2 Caractéristique idéale

IV.1.3 Courant de fuite de la jonction

IV.1.4 Claquage de la jonction

IV.1.5 L’instabilité thermique

IV.1.6 L’effet tunnel

IV.1.7 La multiplication par avalanche

IV.2 Caractéristique statique courant-tension I(V)

IV.3 Dysfonctionnement et Critère de défaillance

IV.3.1 Réduction de la tension de claquage

IV.3.2 Augmentation du courant de fuite

IV.3.3 Critère de dégradation

V. Conclusion

Références Bibliographiques

Chapitre III : Robustesse ESD de la diode de protection, Contrainte non répétée

I. Introduction

II. Robustesse ESD des diodes de protection bidirectionnelles

II.1 Robustesse : Définition et Caractérisation

II.2 Résultats expérimentaux : Influence des paramètres de dessin

II.2.1 Eloignement des jonctions

II.2.2 Impact de la polarisation de la jonction

II.2.3 Résistance interne RS et robustesse de la structure VESD0

II.2.4 Etude de la surface des jonctions

II.3 Conclusion

III. Caractérisation électrique de la défaillance

III.1 Influence de la méthode de caractérisation

III.2 Incrémentation et répétition des décharges

IV. Analyse physique de la défaillance

IV.1 Méthode de localisation

IV.1.1 EMMI et OBIRCh

IV.1.2 Révélation chimique

IV.2 Nature de la défaillance

IV.3 Analyse FIB de la défaillance

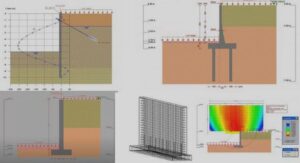

V. Compréhension des phénomènes physiques : simulation électrothermique

V.1 L’outil de simulation Sentaurus WorkBench

V.1.1 Sentaurus WorkBench: Simulation technologique

V.1.2 Emulation du procédé de fabrication de la diode

V.1.3 Maillage de la structure

V.2 Réponse électrothermique du composant

V.3 Mécanisme de dégradation en impulsion unique

VI. Conclusion

Références bibliographiques

Chapitre IV : Fiabilité de la diode vis-à-vis des décharges répétitives

I. Introduction

II. Tenue en répétitif de la diode bidirectionnelle

II.1 Conditions expérimentales

II.1.1 Choix du niveau de tension

II.1.2 Reproductibilité des impulsions

II.1.3 Echantillonnage

II.1.4 Impact de la fréquence de répétition

II.1.5 Polarisation

II.2 Résultats de caractérisation en répétitif

II.2.1 Influence de la distance entre jonctions

II.2.2 Géométrie

II.3 Conclusion

III. Etude statistique de la tenue en répétitif

III.1 Rappel de formalisme mathématique :

III.2 Résultats de caractérisation

III.2.1 Paramètres expérimentaux

III.2.2 Résultats d’endurance

III.2.3 Analyse statistique

III.3 Conclusion

IV. Caractérisation des défaillances ESD

IV.1 Localisation et nature des défaillances

IV.1.1 Défaillance physique

IV.1.2 Dégradation électrique de la diode

IV.1.3 Discussion

IV.2 Corrélation des défaillances électrique et physique

V. Mécanisme de dégradation de la diode de protection dans le mode répétitif

V.1 Simulation électrothermique

V.2 Mécanismes de dégradation

V.2.1 Diode circulaire entourée

V.2.2 Diode circulaire latérale

VI. Optimisation: Implémentation d’une couche barrière

VI.1 Modification de la structure

VI.2 Résultats expérimentaux

VI.2.1 Caractérisation physique

VI.2.2 Etude de la tenue en répétitif

VII. Conclusion