The proliferation of wireless standards and the diminution of radio-terminals’ size at the same time is pushing towards the materialization of newly created concept of software defined radio (SDR). This communication system is expected to realise multiband, multimode radio terminals by defining radio functionality in software [1]. This way, the radio terminal is adapted to different protocols and customized for diverse services by just reprogramming the radio functionality.

This, however, makes the RF-receiver design a challenging task. In an ideal SDR, the solution for increasing both the receiver integration and reconfigurability is provided by transferring the analog-to-digital-conversion interface from the baseband to RF i-e just after the antenna. The inherent advantage of this scheme is that the digital signal processing eliminates the non-idealities associated with analog signal processing i-e device noise and non-linearities, components mismatch etc. The evolution of CMOS technologies towards smaller transistor feature sizes also favours an increased level of digital signal processing in receiver implementation [2].

Nowadays the DSP can operate at a very high frequency and can thus process high frequency signals. The boundary between the RF front-end and the digital baseband is moved to higher frequency, but not yet at RF frequency. The major bottleneck is the design of analog-to-digital-converter (ADC) which can convert the signal at high frequencies. With the current CMOS technologies, it is practically not possible to design an ADC which converts the signal directly at RF.

However, the processing has to be carried out as much as possible in digital due to the low costs, reconfigurability possibility and stability. To go forward in this direction, sub-sampling receiver was proposed. The RF signal is sub-sampled as soon as possible. The frequency downconversion is carried out by the sub-sampler with discrete-time signal processing. One special case of RF receiver which uses discrete-time subsampling is Fs/2 IF receiver [3, 4]. This architecture downscales the frequency from RF to an IF of Fs/2 (one-half of the sampling frequency), thereby making High-Pass (HP) ∆Σ modulator the natural choice for ADC. This ADC is of much reduced complexity as compared to Band-Pass (BP) ∆Σ modulator .

Besides the advantage of converting directly at IF, HP ∆Σ modulator has the potential to efficiently eliminate the dc-offsets and low-frequency noises like flicker noise [5, 6, 7] which are a source of concern in traditional LP ∆Σ modulators. This feature is particularly interesting for time-interleaved ∆Σ converters where the channel-offset is sufficiently removed by HP operation [8], and a simple digital channel equalization technique would minimize effectively the channel gain mismatch effect [30].

Inspite of these potential advantages, the concept of HP ∆Σ modulation has not received much attention, mostly due to its difficult implementation and the uncertainty about its stability and performance in the presence of circuit nonidealities. The basic hindrance block has been the implementation of high pass filter, which is analogous to an integrator in LP ∆Σ modulator. The traditional implementation involves a feedback loop around an integrator and is an expensive solution because of increased power consumption and surface area. However, recently a new architecture of HP filter has been proposed, which gets rid of the drawbacks of the traditional one and hence propels a renewed interest in HP ∆Σ modulators.

Keeping in view its potentials, this thesis is focused on HP ∆Σ modulator in general and its application to multi-mode wireless receivers in particular. Our objectives consist of studying its principle, its performance and stability and comparing it to LP modulators on one hand and applying it to achieve multi-modal wireless receiver functionality on the other.

To achieve these objectives, a new unity signal-transfer-function (STF) single-loop HP ∆Σ modulator architecture has been proposed. It is then used to construct a HP generalized-multi-stage-closed-loop (GMSCL) architecture. The proposed HP unity STF single-loop modulator provides the specifications of EDGE/GSM standard, while the HP GMSCL structure is used for UMTS/WLAN standards.

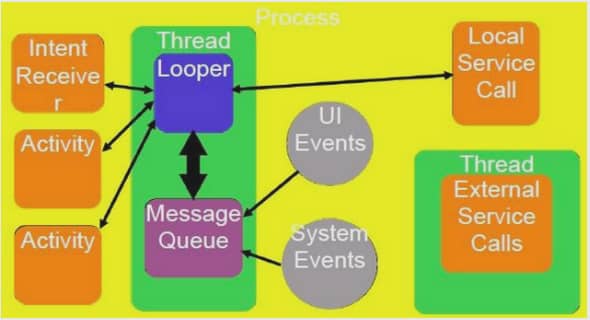

When designing an ADC, it has to be kept in mind that it will be used in what type of RF front-end receiver architecture. Thus the ADC techniques change in accordance with the overall receiver topology. RF front-end receiver is currently defined as the chain of elements from antenna to the ADC. This chain consists of various devices and circuits working at radio frequency band (RF), intermediate frequency band (IF) and analog baseband. ADC is often considered as the boundary between the RF and digital parts of the receiver, but with the advancements in ADCs design which are running at higher and higher sampling rates with each new technology, the ADCs and the associated digital signal processors can now be labelled as IF or even RF devices. Under these circumstances, ADCs and some portion of digital signal processing will soon become a part of RF front-end receiver. Radio receiver architecture choice is driven by many factors, including integration capability, reconfigurability, cost, performance etc. At present, most commercial implementations of RF transceivers are using superheterodyne architecture because of its superior performance compared to other topologies. But the recent advancements in CMOS technologies and integrability of more and more components have triggered interest in the more recent receiver architectures like direct conversion receiver (or zero-IF receiver or homodyne receiver) and low-IF receivers. Direct conversion receiver achieves great cost saving by removing completely the IF portion and providing the gain in baseband section of the receiver which is completely integrable. Multimode operation is also easily supported by direct-conversion receiver without any component addition. The problems inherent in zeoIF receiver have led to the creation of a modified structure called low-IF structure. The wireless receivers based on CMOS technologies have a preference for low-IF architecture because it gets rid of the problems of dc-offset and flicker noise which are serious in CMOS circuits. The latest evolution in the field of wireless receiver design is IF bandpass sampling receiver which uses the principle of subsampling to bring down the RF signal to IF by voluntary aliasing. The factor behind the success of this receiver is the enhancement of the sampling rate and resolution of the ADCs with an acceptable power consumption. This receiver be considered as another step towards the realization of the concept of software radio. An interesting class of this receiver structure is Fs/2 IF receiver which combines the advantages of both direct conversion and low-IF receivers. In this chapter, the various reception schemes are discussed in order of their arrival in the wireless arena i-e Superheterodyne receiver, Digital-IF receiver, Direct Conversion receiver, Low-IF receiver, IF Bandpass sampling receiver and its application to the Fs/2 IF receiver. Special attention is paid to the suitability of these schemes to the ∆Σ modulators in general and high-pass ∆Σ modulators in particular.

1 Introduction |