Modularité en bloc des codes de configuration numérique

Bus WISHBONE

L’architecture de bus WISHBONE est implanté à partir d’un code source en VHDL. Pour faciliter l’expansion et la réutilisation de l’architecture, on a respecté certaines règles recommandées suivantes : – Les fichiers et les modules qui se réfèrent au bus WISHBONE sont nommés en ajoutant le préfixe wb_. – Le module de l’architecture qui gère le bus WISHBONE est labellisé avec le préfixe ma_ pour désigner le « master ». Tandis que tous les autres modules esclaves sont désignés tous avec un préfixe sl_ pour « slave ». Figure-5. 11 : Structure d’un bus intégré WISHBONE Les codes qui instancient les modules majeurs qui constituent l’architecture sont déjà disponibles et contenus dans des fichiers VHDL suivants : wb_syscon.vhd: Cette entité fournis les signaux d’horloge SYSCL et de RESET pour le bus WISHBONE. N.B: le bus WISHBONE est totalement synchrone avec le système de registres tampons “Slave FIFO” du microcontrôleur CY7C68013A. entity wb_syscon is generic ( nr_of_dbgports : positive := 1 ); Chapitre 5 Modularité en bloc des codes de configuration numérique 112 port ( SYSCON_O : out rec_syscon_port; sys_rst_i : in std_logic; sys_clk_i : in std_logic; debug : inout std_logic_vector((nr_of_dbgports-1) downto 0) ); end wb_syscon; architecture RTL of wb_syscon is signal syscon : rec_syscon_port := syscon_default; signal sys_rst : std_logic := ‘1’; signal sys_clk : std_logic := ‘0’; begin — connect ports to internal signals—————————– SYSCON_O <= syscon; sys_rst <= sys_rst_i; sys_clk <= sys_clk_i; debug <= ( others => ‘Z’ ); — architecture implementation —- syscon.rst <= sys_rst; syscon.clk <= sys_clk; end RTL;

Le Bus AXI

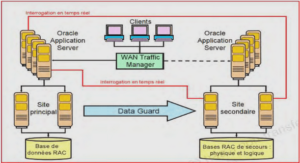

Le système de bus abstrait AXI est la technologie adoptée par Xilinx pour l’interconnexion des Cores IP. Figure-5. 12 : Caractéristiques d’un bus intégré AXI Chapitre 5 Modularité en bloc des codes de configuration numérique 113 Cette structure de bus est disponible dans la configuration des composants ZYNQ série-7000 est a été étudié pour la migration du système d’acquisition utilisant le ZEDBOARD. Figure-5. 13 : Implantation du bus intégré AXI sur le processeur ZYNQ ZYNQ-VIVADO Plusieurs modules d’interface AXI sont disponibles sur la plateforme VIVADO de Xilinx pour le développement du projet avec le ZEDBOARD. Figure-5. 14 : Modules IP disponibles sur VIVADO Chapitre 5 Modularité en bloc des codes de configuration numérique 114 Le module IP AXI interconnect est utilisé pour interfacer le module IP « Zynq Processing system » avec le module IP Xilinx sg_filter, module abstrait construit à partir de MATLAB. Figure-5. 15 : Module IP AXI implanté dans le projet de construction du système de traitement des signaux numériques sur ZYNQ Le module d’interface IP « AXI-Interconnect » possède toutes les ressources nécessaires pour la séquence et le protocole pour la gestion des données, telles que l’horloge, les ports d’interface des données. Figure-5. 16 : Ressources disponibles pour le module IP AXI