Evolution des circuits intégrés

La microélectronique a connu une fantastique évolution depuis l’invention du premier circuit intégré en 1958 par l’Américain Jack Kilby. Cette évolution suit la loi de Moore, qui prévoit que tous les 18 mois, le nombre de transistors sur une même surface de silicium double. Ainsi la technologie d’intégration a évolué de l’échelle SSI (Small Scale Integration) avec moins de 12 portes par boîtier, à l’échelle ULSI (Ultra Large Scale Integration) avec plus de 105 portes. Ce résultats est devenu possible grâce à la réduction des tailles de lithographie qui caractérisent les longueurs minimales des canaux des transistors, mais aussi grâce à l’amélioration des procédés de fabrication des circuits intégrés.

Alors que cette évolution a permis un énorme essor technologique en rendant possible la construction de circuits performants en termes de vitesse d’exécution et de consommation d’énergie, elle s’accompagne de plusieurs contraintes. C’est le cas d’inter-compatibilité entre d’un côté les différents blocs d’un même circuit et d’un autre côté entre les circuits intégrés sur une même carte.

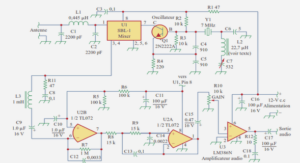

Pour faire face à ces contraintes, une des solutions envisagées vise à réduire les longueurs des interconnexions entre circuits en les rapprochant. Des nouvelles méthodes d’intégration sont désormais utilisées, comme l’intégration sur puce ou System on Chip (SoC), et l’intégration sur boîtier ou System in Package (SiP). Cependant, l’augmentation du niveau d’intégration s’est accompagnée de plusieurs changements au niveau des caractéristiques des circuits intégrés, qui impactent directement le comportement électromagnétique de ces derniers.

D’abord, l’augmentation des fréquences de fonctionnement et l’accroissement de la complexité de conception implique une augmentation à la fois des niveaux des émissions parasites, mais aussi la diminution de l’immunité des composants électroniques.

Ensuite, l’amélioration de la consommation des circuits a une influence sur l’immunité. En effet, la diminution des tensions d’alimentations augmente la vulnérabilité des circuits face aux agressions électromagnétique, à cause de la réduction des seuils de commutation et des marges de bruit, ce qui se traduit par des niveaux d’immunité plus bas.

Tous ces paramètres doivent être pris en considération lors de la conception des systèmes électroniques mais aussi des circuits intégrés, afin de bien estimer les performances des équipements.

Influence des perturbations sur le comportement des circuits intégrés

Les perturbations électromagnétiques impactent fortement les performances d’un système électronique. Cela dit, les effets observés varient suivant la nature du circuit. Ainsi, le comportement des circuits numériques à ces perturbations est sensiblement différent de celui des circuits analogiques.

Pour un circuit analogique, l’apparition des effets de la perturbation, comme un décalage du signal utile ou une fluctuation de tension d’alimentation, varie en fonction du mode de fonctionnement dans la bande de fréquence du composant et hors bande.

Cependant, ces conséquences présentent un caractère temporaire. Une fois la perturbation disparue, le comportement du composant redevient souvent nominal. Pour les composants numériques ce n’est pas forcément le cas.

En effet, plusieurs phénomènes dûs notamment aux perturbations électromagnétiques peuvent être observés pour ce type de circuit intégré. Le phénomène de latchup : Ce phénomène correspond à la mise en conduction d’un thyristor (structure PNPN) parasite présent dans tous les circuits intégrés de technologie CMOS entre l’alimentation et la masse .

Il crée un chemin de conduction parasite direct entre la masse et l’alimentation. Il cause par conséquent un échauffement supplémentaire important dans le circuit et entraîne une forte augmentation de la consommation. Le court circuit engendré peut conduire à la destruction du circuit si le courant de l’alimentation n’est pas contrôlé.

Modélisation de l’immunité conduite des circuits intégrés et des cartes électroniques

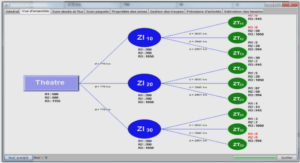

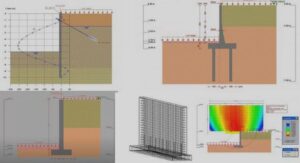

Le phénomène de l’immunité conduite se caractérise par le dysfonctionnement d’une fonction électronique soumise à des perturbations électromagnétiques conduites sur ses connections. Il repose sur les mêmes éléments dans les deux cas de figures : circuits intégrés ou cartes électroniques. Ce modèle est constitué d’une impédance d’entrée PDN (comme pour les modèles d’émissions conduites), et un étage d’immunité IB (Immunity Behaviour) qui représente la réponse du sujet de test aux perturbations.

Le modèle CEM de l’immunité conduite au niveau circuit intégré existe déjà. Il est désormais une norme (IEC62433-4) pour la simulation de l’immunité conduite. Ce modèle s’inspire fortement du modèle d’émission conduite. Il a été mis en œuvre pour la modélisation de plusieurs types de composants de niveaux de complexité différents.

Comme pour le modèle d’émissions conduites, le modèles d’immunité conduite au niveau carte électronique est toujours au stade de projet. Il reprend également la même logique, à savoir l’utilisation des modèles d’immunité des composants d’une carte et les combiner afin de construire un modèle complet de cette dernière.

La norme BCI

La méthode de mesure Bulk-current injection (BCI) est largement utilisée pour caractériser l’immunité conduite des systèmes électroniques et spécifiquement dans le domaine de l’automobile. Cependant, son application aux circuits intégrés n’est pas simple. Généralement, cette injection est appliquée à des câbles reliés à une carte de test CEM, où se trouve le circuit intégré. La perturbation est indirectement injectée dans le circuit sous test (DUT) à travers les câbles et le PCB à l’aide d’une pince de couplage inductif. La seconde pince permet de mesurer le courant effectivement injecté dans le câble de test, par conséquent, c’est cette valeur qui est considérée lorsque le point de défaillance est atteint.

Selon la norme actuelle, l’agression couvre les fréquences de 10 kHz à 400 MHz avec un signal agresseur de type CW ou AM et des valeurs de courant injecté variant selon le degré de sévérité souhaité. Cette limitation est due aux caractéristiques de la pince d’injection.

En ce qui concerne les point négatifs, il faut noter que la mise en œuvre elle-même a une forte influence sur le résultat de la mesure de l’immunité, en raison de la résonances des câbles et des pistes du PCB. De ce fait, toute mesure est précédée par une phase de calibrage de la pince d’injection, durant laquelle on mesure le courant produit dans une résistance de 100 Ω pour une puissance déterminée. Ce courant servira de référence de mesures.

Un autre point négatif est que la génération du courant perturbateur demande une puissance considérable. En effet, la valeur du couplage de la pince d’injection est très faible, à peine 10% de la puissance injectée dans la pince inductive sert à créer le courant perturbateur. Ce choix est intentionnel dans le but de limiter l’influence de la pince d’injection sur le câble de test.

Table des matières

1 Introduction générale

2 Généralités sur la compatibilité électromagnétique et la CEM des circuits intégrés

2.1 Généralités sur la compatibilité électromagnétique

2.1.1 Introduction

2.1.2 Sources des perturbations électromagnétiques

2.1.2.1 Sources intentionnelles

2.1.2.2 Sources non intentionnelles

2.1.3 Couplage des perturbations électromagnétiques

2.1.3.1 Couplage rayonné

2.1.3.2 Couplage conduit

2.2 CEM des circuits intégrés

2.2.1 Evolution des circuits intégrés

2.2.2 Emissivité des circuits intégrés

2.2.2.1 Origine des émissions parasites des circuits intégrés

2.2.2.2 Méthodes normalisées de mesure de l’émission des circuits intégrés

2.2.2.3 Modélisation de l’émission conduite des circuits intégrés et des cartes électroniques

2.2.3 Immunité des circuits

2.2.3.1 Influence des perturbations sur le comportement des circuits intégrés

2.2.3.2 Méthodes normalisées de mesure de l’immunité des circuits intégrés

2.2.3.3 Techniques d’amélioration de l’immunité des systèmes électroniques

2.2.3.4 Modélisation de l’immunité conduite des circuits intégrés et des cartes électroniques

2.3 Conclusion

3 Méthodologie de mesure de l’immunité conduite pour les circuits intégrés complexes

3.1 Introduction

3.2 Modèle existant

3.2.1 La norme BCI

3.2.2 La norme DPI

3.2.3 Composants étudiés

3.2.3.1 Présentation générale

3.2.3.2 Protocole SPI

3.3 Caractéristiques d’injection

3.3.1 Critère d’immunité

3.3.1.1 Critère fonctionnel

3.3.1.2 Critère électrique

3.3.2 Chemin de couplage

3.3.2.1 Conception et contraintes du multiplexeur RF/BB

3.3.2.2 Conception des pistes et des transitions

3.3.2.3 Simulations et mesures des caractéristiques du multiplexeur

3.3.2.4 Validation du multiplexeur : Étude détaillée sur l’inverseur SN74LS04D

3.3.3 Système de mesure

3.3.3.1 Interface de communication et de contrôle

3.3.3.2 Carte de test

3.3.3.3 Mise en œuvre du système de mesure

3.3.4 Logiciel de gestion et algorithme de mesure

3.3.4.1 Algorithme de mesure

3.3.4.2 Logiciel de gestion

3.3.4.3 Banc d’agression conduite

3.4 Résultats de mesure et discussions

3.4.1 Immunité et critère de test

3.4.2 Immunité et fréquence de communication SPI

3.4.3 Immunité et phase d’accès mémoire

3.4.4 Immunité et technique de conception

3.4.5 Immunité et broche d’injection

3.5 Conclusion

4 Méthodologie de construction d’un modèle d’immunité pour la gestion de l’obsolescence

4.1 Introduction

4.2 Modélisation niveau composant

4.2.1 Modèle d’émission ICEM-CE

4.2.2 Modèle de susceptibilité ICIM-CI

4.2.2.1 Présentation de la norme

4.2.2.2 Composant PDN

4.2.2.3 Composant IB

4.2.3 Développement du modèle ICIM-CI pour les mémoires

4.2.3.1 Structure du modèle

4.2.3.2 Extraction et modélisation du PDN

4.2.3.3 Extraction du IB

4.2.3.4 Validation du modèle

4.3 Prédiction de l’immunité d’une carte électronique dans le cas d’un changement de composant

4.3.1 Modélisation niveau carte

4.3.1.1 Modèle EBIM-CI

4.3.2 Procédure de modélisation

4.3.2.1 Présentation de l’application étudiée

4.3.2.2 Présentation générale de la procédure

4.3.2.3 Extraction du modèle

4.3.2.4 Simulation et validation du modèle

4.4 Conclusion

5 Conclusion générale

Listes des publications

Bibliographie