L’amplificateur d’instrumentation

Les signaux captés par les électrodes étant particulièrement faibles, des amplificateurs de hautes performances (gain, linéarité, différentialité, minimum de bruit de fond) sont nécessaires.

Le rôle de l’amplificateur d’instrumentation est le même que celui de l’amplificateur de différence. Cependant, on choisira :

– l’amplificateur de différence si la source d’entrée est à faible impédance

– l’amplificateur d’instrumentation si la source d’entrée est à grande impédance

Dans notre cas, on cherche à visualiser l’activité électrique du cœur de l’ordre de (mV). Un Amplificateur d’Instrumentation est donc nécessaire pour extraire efficacement ce signal.

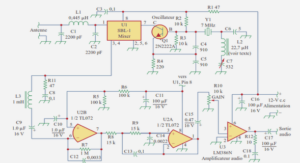

De ce fait, on choisira un amplificateur d’instrumentation avec structure à trois amplificateurs opérationnels. Le schéma du montage est sur la figure 4.4.

Les entrée-sorties de la carte d’acquisition « Fusion Embedded Developpment Kit » d’Actel

Apres les différents conditionnements du signal analogique acquis par une carte fille que l’on vient de réaliser (amplification et filtrage du signal analogique acquis par les électrodes), on obtient un signal prêt à être transformé en signal numérique par le convertisseur analogique numérique intégré dans la carte d’acquisition d’Actel. La sortie de la carte fille est donc directement reliée à l’entrée analogique de la carte » Fusion Embedded Developpment Kit « .

Le convertisseur analogique numérique intégré dans la carte

« Fusion Embedded Développement Kit » d’Actel

Actel Fusion® est la première famille de FPGA à signaux mixtes. Fusion inclut un convertisseur analogique-numérique (CAN) avec une entrée analogique configurable 32:1 d’un multiplexeur. Le CAN prend en charge un mode de fonctionnement à 8 -, 10 – et 12-bits avec un taux cumulatif de l’échantillon jusqu’à 600 kbps pour un mode de fonctionnement à 8- bits. Par défaut, lorsque les utilisateurs configure la séquence d’échantillons à l’aide de l’Analog System Builder (ASB) du logiciel Libero® Integrated Design Enviroment (IDE), toutes les canaux des entrées analogiques actives partagent la bande passante du CAN (débit) de manière uniforme. Le débit du CAN de Fusion est déterminé par deux éléments: le temps de conversion t_conv – le temps nécessaire à l’acquisition associé ou de l’échantillon, et le temps nécessaire pour faire la conversion réelle, et le délai d’exécution t_turnaround-le temps nécessaire pour traiter les données et de donner un signal de départ pour une autre conversion.

Le convertisseur analogique numérique intégré dans la carte » Fusion Embedded Developpment Kit » est illustré par la figure 4.9. Le CAN Complet est illustré à l’ANNEXE I.

Extraction des paramètres ECG et calcul du pouls par le FPGA

La sortie du circuit d’acquisition de l’ECG analogique est connectée directement surune carte FPGA. L’algorithme numérique mis en œuvre sur le FPGA vise à détecter les points R et calculer le pouls en temps réel. L’approche mise en œuvre sur la carte FPGA commence avec un filtre « moving average » pour éliminer le bruit des hautes fréquences. Puis, il est suivi par la détection du point R et le calcul de la fréquence cardiaque. L’algorithme numérique détaillé est illustré sur la figure 4.11:

Interfaçage FPGA- PC

L’interfaçage de la carte Fusion Embedded Developpment Kit avec le PC est réalisée avec un câble USB physique mais la nature de la connexion est une connexion port série virtuelle. Pour faire en sorte de communiquer le FPGA avec le PC, on a besoin d’installer un pilote sur le PC pour émuler un port série alors que physiquement c’est un port USB. C’est un pilote que l’on peut télécharger sur le site d’Actel, connu sous le nom de CP2102. Le protocole utilisé est le protocole UART. Pour le FPGA un core que l’on appelle core UART se charge de communiquer les données dans le FPGA vers un PC.

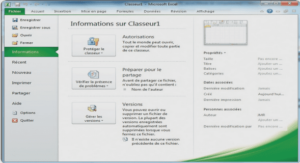

Le flot de conception de Libero IDE

De la conception du programme à introduire dans le circuit programmable FPGA jusqu’à sa programmation, toutes les étapes à réaliser suivent le flot de conception du logiciel Libero IDE. La conception et la programmation de notre plateforme Biomedicalscope ont été donc réalisé suivant le procédé dans ce flot de conception. Ceci est illustré dans la figure 4.15.

Approche de conception par schéma

Cette partie porte sur la conception de l’ECG numérique à l’aide de l’approche de conception FPGA par schéma. Dans cette partie, notre projet d’instrumentation biomédicale présente une structure hiérarchique reposant sur des modules schématiques. En effet, le fichier top level du projet contient une représentation schématique de l’ensemble du système qui fait appel à plusieurs types de macros de niveaux inférieurs. Ces macros utilisent plusieurs types de modules de natures variées dont des modules schématiques, des IP générés à l’aide du « Core Generator », des modules paramétrées générées à l’aide du « SmartGen Core » de

Libero IDE et des modules VHDL. Dans cette section, voyons successivement les étapes suivantes : la création du schéma top level de l’ECG, la simulation fonctionnelle, l’implémentation du projet, la simulation avec timing et la configuration du FPGA avec le système conçu.

Création d’un schéma top level

Le schéma top level permettra d’instancier plusieurs modules de niveaux hiérarchiquesinférieurs et d’interconnecter le tout pour réaliser le schéma complet de l’ECG numérique. Les blocs : CoreAI, Oscillateur RC, PLL sont des périphériques « Hard IP » tandis que les autres blocs représentent des périphériques « Soft IP ».

Simulation fonctionnelle avec Modelsim

Une fois l’étape de conception terminée, nous allons effectuer une simulation fonctionnelle du projet à l’aide d’un testbench et du simulateur Modelsim. Pour ce faire, nous allons d’abord générer un fichier testbench VHDL à l’aide du Navigateur de projet Libero IDE. Ensuite, nous configurerons et lancerons notre simulation Modelsim à partir du Navigateur Libero IDE. Une fois appelé par Libero IDE, Modelsim prendra en charge la simulation et la présentation des résultats.

Implémentation du projet

Dans cette étape, nous effectuerons la synthèse et l’implémentation du projet Biomedicalscope. Nous créons d’abord des contraintes de timing et les incorpore au projet. Nous spécifierons ensuite la configuration des broches d’entrées/sorties à adopter et nous générerons enfin le fichier de programmation du FPGA M1AFS1500-FGG484. L’implémentation du projet consiste à effectuer les étapes d’interprétation (translation), de mapping, de placement et routage et de génération du fichier de programmation. Tous les outils d’implémentation du projet sont d’ailleurs intégrés au Navigateur Libero IDE.

LA PARTIE SOFTWARE DU PROJET

Synoptique générale du logiciel

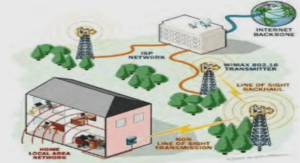

L’architecture générale de la plateforme est composée de plusieurs étages de traitement et est constituée de plusieurs éléments matériels et logiciels. Après l’étage d’acquisition et de prétraitement du signal ECG, le signal va être envoyé dans un PC pour y être stocké, visualisé, analysé et envoyé vers un autre PC client à travers un réseau pour permettre le télé-monitoring du signal ECG. Cette partie traitera donc la réalisation du logiciel qui prendra en charge la gestion des fonctionnalités énoncées précédemment mais servira surtout d’interface entre la plateforme et son utilisateur. La typologie de l’application sera une architecture client serveur de type I, selon les spécifications du Gartner Group qui a proposé une typologie des applications client-serveur qui sert de référence dans le développent de ce genre de logiciel. Les éléments qui composeront l’application c’est-à-dire les données, le traitement, et la présentation seront réparties sur le poste client et le poste serveur.

Conception

La plupart des nouveaux langages sont orientés objet et c’est UML qui nous a permis de faire la conception de notre application.

Dans l’optique de concevoir un système qui soit modulaire, facilement extensible et orienté objet, le langage de modélisation UML s’est imposé comme l’outil le plus approprié pour la modélisation de ce projet.

De nos jours UML2 possède treize diagrammes qui sont classés en deux catégories (dynamique et statique). Mais pour la conception du logiciel on peut voir les diagrammes de cas d’utilisation du logiciel.

Diagrammes de cas d’utilisation

Un diagramme de cas d’utilisation permet d’avoir une vue globale de l’application et de décrire les interactions entre les acteurs dans chacun des cas d’utilisation envisagés. Le diagramme suivant montre les acteurs du système et les différentes possibilités d’utilisation du logiciel.

Implémentation

Comme dit plus haut dans la description de l’architecture de l’application, celle-ci sera implémentée dans un poste serveur et dans un poste client.

Fenêtre de chargement de l’application

Une fenêtre d’attente (Figure 4.24) a été implémentée pour le chargement du logiciel. C’est cette fenêtre qui s’affiche en premier lors du lancement du logiciel.