Introduction des oxydes à grande permittivité dans les dispositifs de la nanoélectronique

Films minces d’oxydes à grande permittivité pour la nanoélectronique

Contexte technologique : la miniaturisation

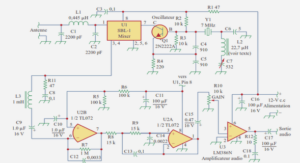

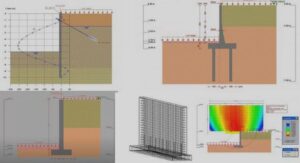

La course à la miniaturisation du transistor a induit différents axes de recherche de solutions technologiques. Ces choix technologiques ont été guidés par la nécessité de toujours augmenter le courant de saturation dans l’état ON du transistor. Ce courant est défini par la relation suivante : 13 2 )( 2 G T ox G on VV S C L Z I = μ − (1.01) où μ est la mobilité des porteurs dans le canal, Z la largeur de grille, LG la longueur de grille, VG la tension entre la source et la grille, VT la tension de seuil (tension à partir de laquelle le courant passe dans le transistor), Cox la capacité du transistor et S la surface en contact entre le substrat et l’oxyde de grille et entre l’oxyde de grille et la grille. Les trois voies suivantes, qui ont été explorées avec succès, sont discutées dans la suite (Figure 1-6) : • réduction de la longueur de grille LG ; • augmentation de la mobilité des porteurs μ dans le canal ; • augmentation de la densité de capacité Cox/S. Figure 1-6 : localisation des trois paramètres qui permettent d’optimiser les performances du transistor (densité de capacité Cox/S, longueur de grille LG et mobilité des porteurs µ).

Réduction de la longueur de grille LG

Historiquement, c’est le paramètre qui a dominé la miniaturisation. La photolithographie est actuellement le procédé le plus répandu pour délimiter l’extension latérale des composants sur le substrat semiconducteur. Grâce à l’amélioration continue des techniques de photolithographie, LG est passé sous la barre des 100 nm au début des années 2000 et est aujourd’hui en production en 60 voire 45 nm. Pour améliorer la résolution de cette technique, des photons de faibles longueurs d’onde, dans le domaine de l’ultraviolet profond, sont utilisés.

Augmentation de la mobilité des porteurs μ dans le canal

L’augmentation de la mobilité des porteurs dans le canal permet d’accroître la vitesse de transmission de l’information, via l’augmentation de la fréquence de coupure au-delà de laquelle le transistor n’est plus capable de fonctionner correctement. L’industrie de la microélectronique vise l’obtention de fortes mobilités pour de faibles champs effectifs. Considérons les variations de la mobilité des porteurs en fonction du champ appliqué pour le silicium (Figure 1-7 (a)). Sous champs faibles, les mobilités obtenues tant pour les trous que pour les électrons sont en général médiocres en grande partie à cause des collisions des porteurs sur les états d’interface canal/diélectrique. Plusieurs solutions ont été successivement envisagées pour améliorer les mobilités : • l’introduction de contraintes biaxiales, résultant de la croissance épitaxiale de Si ou de Ge sur des substrats de type SiGe. La Figure 1-7 (a) montre les gains de mobilité obtenus en utilisant du Si ou du Ge contraints (s-Si et s-Ge) ; • l’introduction de contraintes uniaxiales dans la direction source-drain permet un gain nettement plus important (Figure 1-7 (b)). Notons que ceci n’est pas obtenu par croissance mais via l’architecture du transistor, par exemple en utilisant des sources et drains en alliages SiGe.

La direction cristallographique selon laquelle la contrainte est appliquée doit être judicieusement choisie de façon à privilégier le type de porteur (lourd ou léger) contrôlant la mobilité ; (a) (b) Figure 1-7 : (a) mobilité des porteurs dans le cas du silicium et du germanium, éventuellement contraints (s-) [Halimaoui2007] et (b) une compression uniaxiale est plus favorable qu’une tension biaxiale pour l’augmentation de la mobilité des porteurs [Thompson2006]. 15 • le remplacement du silicium par un matériau offrant des mobilités de porteurs intrinsèquement supérieures, comme par exemple le germanium ou les matériaux III-V (Tableau 1-1). Cette solution est actuellement étudiée en laboratoire mais pose d’énormes problèmes de compatibilité de procédés, en site industriel. Si Ge GaAs InSb InP Paramètre de maille (nm) 0,543 0,565 0,565 0,648 0,587 Largeur de la bande interdite (eV) 1,12 0,66 1,42 0,17 1,35 Mobilité des trous (cm2 .V-1 .s -1) 450 1 900 400 1 250 150 Mobilité des électrons (cm2 .V-1 .s -1) 1 500 3 900 8 500 80 000 4 600 Constante diélectrique 11,9 16,0 13,1 17,7 12,4 Point de fusion (°C) 1412 937 1240 527 1060 Tableau 1-1 : propriétés des semiconducteurs proposés comme alternative au Si pour la fabrication d’un canal de transistor MOS. Avec l’introduction des diélectriques à grande permittivité, un regain d’intérêt s’est développé particulièrement pour le germanium, matériau initial du transistor MOS.

Le germanium se trouve dans la même colonne de la classification périodique (IVA) que le silicium et présente donc des propriétés similaires. Son principal avantage par rapport au silicium réside dans la mobilité des électrons et des trous très augmentée, respectivement des facteurs 2,6 et 4,2 [Kamata2008]. L’application de contraintes adaptées comme pour le silicium permettra d’améliorer encore ces mobilités [Fischetti1996]. Notons que la mobilité des trous dans le Ge est la plus élevée de toutes celles des matériaux semiconducteurs des groupes IV et III-V (Tableau 1-1).

En revanche, la mobilité des électrons dans le germanium reste inférieure à celles des semiconducteurs III-V. Au-delà des propriétés discutées ci-dessus, intrinsèques au substrat semiconducteur, il ne faut pas oublier la réduction de la mobilité des porteurs dans le canal que peut introduire le remplacement de l’oxyde de grille, la silice, par un oxyde diélectrique de grande permittivité (cf I-B.3) associé à une grille métallique (cf III). Trois mécanismes distincts sont à considérer [Robertson2006] : • les interactions coulombiennes avec les charges piégées dans l’oxyde de grille et aux interfaces avec le substrat et la grille ; • les interactions avec les imperfections de surface (rugosité de l’interface semiconducteur/diélectrique de grille) ; • les interactions entre les phonons de l’oxyde de grille et les porteurs du canal. 16 I-B.3 Augmentation de la densité de capacité Cox/S La densité de capacité du dispositif s’exprime en fonction de la constante diélectrique de l’oxyde et de son épaisseur : S t C κ o ε = (1.02) où ε0 est la permittivité du vide, κ celle de l’oxyde de grille, t l’épaisseur de l’oxyde et S la surface en contact entre la grille et le substrat.

REDUCTION DE L’EPAISSEUR DE L’OXYDE DE GRILLE

L’augmentation de la densité de capacité de l’oxyde de grille a été obtenue jusqu’à ces dernières années en réduisant son épaisseur (cf 1.02). Ceci a été possible grâce à l’utilisation de la silice amorphe, matériau de grande qualité aux propriétés électriques excellentes. En effet, la silice possède une importante largeur de bande interdite (9 eV) et un grand décalage de bandes de conduction CBO (Conduction Band Offset) et de valence VBO (Valence Band Offset) avec le silicium, respectivement 3,5 eV et 4,4 eV. Il est possible de la faire croître sur le silicium par oxydation thermique avec un excellent contrôle de son épaisseur et de son uniformité.

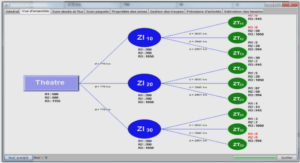

De plus, la silice forme naturellement une interface stable avec le silicium avec une faible densité d’états d’interface intrinsèques. La réduction de l’épaisseur de l’oxyde de grille a progressé ainsi avec succès pendant 30 ans. Aujourd’hui, les générations de transistors nécessitent des épaisseurs de silice inférieures au nanomètre (Figure 1-8), ce qui la rend inutilisable. Deux raisons en sont la cause. D’une part, pour les films très minces (typiquement d’épaisseur inférieure à 3 nm), les porteurs de charges peuvent traverser le diélectrique par un mécanisme d’effet tunnel dont la probabilité croît exponentiellement avec la diminution d’épaisseur de l’oxyde.

Le courant tunnel augmente d’un ordre de grandeur pour chaque diminution de l’épaisseur de l’oxyde de 0,2 nm [Ghani2000]. Ainsi, si nous considérons que la limite de courant tunnel acceptable pour un dispositif hautes performances est de 10-5 A/cm2 et pour un dispositif à faible puissance de 10-2 A/cm2 , alors les épaisseurs limites de silice sont respectivement ~ 1,4-1,6 nm et ~ 2 nm [Lucovsky2005] (Figure 1-8). Par ailleurs, un travail remarquable de spectroscopie de pertes d’énergie d’électrons a défini la valeur 0,7 nm comme la limite physique au-delà de laquelle SiO2 perd les propriétés électroniques du matériau massif 17 [Muller1999].

Diminuer l’épaisseur physique de l’oxyde de grille en deçà d’une certaine limite n’est donc plus un choix acceptable pour l’amélioration des futurs dispositifs. Figure 1-8 : prévisions pour l’épaisseur équivalente d’oxyde d’après l’ITRS 2003 [Wong2006]. CONSTANTE DIELECTRIQUE ET EOT Compte-tenu de la relation 1.02, une autre voie évidente pour continuer à augmenter la densité de capacité consiste à trouver un nouveau matériau d’oxyde de grille de permittivité plus élevée que celle de la silice. Ce choix permet de conserver une épaisseur d’oxyde physiquement acceptable pour éviter les effets tunnels directs entre la grille et le substrat. Depuis plusieurs années, les travaux de recherche se sont donc orientés vers la définition, la préparation et le contrôle des propriétés de films minces d’oxydes à grande constante diélectrique [Wilk2001]. Pour comparer un matériau à grande constante diélectrique à la silice, la notion d’épaisseur équivalente d’oxyde EOT (Equivalent Oxide Thickness) a été introduite.

Elle définit l’épaisseur qu’aurait la silice de même capacité que celle d’un matériau de constante diélectrique κhigh-κ et d’épaisseur physique thigh-κ : κ κ κ κ − − == high high SiO SiO ttEOT 2 2 (1.03) Remplacer la silice par un oxyde de constante diélectrique κ permet d’augmenter l’épaisseur physique de la couche de diélectrique d’un facteur κ/3,9 tout en conservant, voire en améliorant, la capacité du condensateur. A titre d’exemple, une constante diélectrique 18 comprise entre 8 et 60 permet des accroissements d’épaisseur d’un facteur compris entre 2 et 15 et donc permet de réduire le courant tunnel de plusieurs ordres de grandeur. Cependant, l’intégration d’un oxyde à grande permittivité dans une architecture MOS occasionne plusieurs effets importants qui conditionnent les performances du dispositif.

Ces oxydes alternatifs à base d’éléments de transition et de terres rares (cf chapitre 2) induisent la formation inévitable à l’interface avec le substrat semiconducteur d’une couche de faible permittivité qui nuit à l’EOT de l’empilement et qu’il est nécessaire de contrôler. Ce point sera développé au chapitre 2 I-E sur la base de résultats bibliographiques puis illustré et discuté dans le cas particulier de chaque film mince étudié dans les chapitres 4, 5 et 6. Par ailleurs, ces films sont cristallins pour la plupart, au moins après l’étape de recuit à très haute température nécessaire au procédé de fabrication du MOS. Stabiliser la phase de plus grande permittivité devient donc impératif. Ce point sera aussi développé au chapitre 2 I-C puis illustré dans le cas particulier de chaque film mince étudié dans les chapitres 4, 5 et 6. Enfin, la nécessité d’introduire une grille en métal et non plus en polysilicium dopé sera discutée à la fin de ce chapitre mais n’est pas étudiée dans le cadre de cette thèse. Pour tenir compte de ces différents effets, des définitions relatives aux épaisseurs liées à l’oxyde de grille seront introduites dans le chapitre 3 II-C.1 et utilisées lors de la discussion des résultats des chapitres 4, 5 et 6.

Chapitre 1 : Introduction des oxydes à grande permittivité dans les dispositifs de la nanoélectronique |