Evolution de la microélectronique rencontre avec le quantique

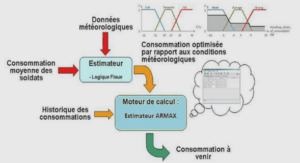

La diminution de la taille des transistors MOSFETs vers l’échelle nanométrique s’accom- pagnedenouveauxeffets électrostatiques et quantiques. Afin de retarder leur apparition, plusieurs stratégies sont envisagées à plus ou moins longue échéance. Ce chapitre se propose de présenter les principaux effets issus de la réduction des dimensions et de décrire les limites des solutions technologiques déjà disponibles (section (1.1)). Nous discutons dans la section (1.3) des structures émergentes de MOSFETs à plusieurs grilles, susceptibles de poursuivre la miniaturisation dans les années à venir. Au delà, les futures générations de transistors pourraient être construites à partir de molécules. La section (1.4) étudie donc en détail le cas prometteur du transistor à nanotubes de carbone pressenti comme le successeur direct du MOSFET. La section (1.5) résume et ouvre sur les perspectives. La croissance de l’industrie des semi-conducteurs dépend pour l’instant de sa capacité à miniaturiser les transistors. L’objectif de la démarche est de délivrer de meilleures performances à moindre coût. Des circuits plus petits réduisent la surface globale de la puce électronique et permettent donc de produire plus de transistors sur un même wafer sans impacter sur le prix de fabrication. Le coût des circuits diminue ainsi d’un facteur deux tous les 18 mois. Les performances électriques des composants sont également améliorées (tableau(1.1)). En diminuant la dimension des MOSFETs, le temps de passage de l’état « off » à l’état « on » diminue linéairement du fait de l’évolution du temps de réponse intrinsèque = longueur de canal/vitesse des porteurs. Un autre avantage est la réduction de la consommation de puissance, utile pour augmenter la durée d’autonomie des systèmes mobiles mais aussi pour améliorer la fiabilité des systèmes hautes performances. Des puces plus petites consomment moins de puissance, donc moins d’énergie est utilisée pour chaque opération. En conséquence, le produit puissance-temps de réponse est réduit. Enfin, la rapidité de transmission de l’information dans un circuit intégré est limitée par la vitesse de l’impulsion électrique. Pour pouvoir augmenter la rapidité globale d’une opération, il faut réduire les distances géométriques, et empiler un maximum de données d’information dans un minimum d’espace pour les rapprocher. Cette évolution permet à un large public d’accéder à des services plus performants, moins chers et souvent nouveaux. Des objets technologiques innovants sont ainsi produits et créent de nouveaux marchés dont les retombées financières sont réinvesties dans la course à l’intégration (figure(1.1)).

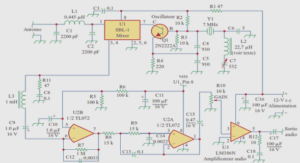

est inférieur au dixième de sa valeur à la tension de seuil. Le paramètre S limite la réduction de la tension de seuil d’un nanoMOSFET puisque le courant à zéro volt, c’est-à-dire le courant de l’état « off » doit rester suffisamment faible pour ne pas consommer de puissance. Il existe actuellement deux structures de composants largement étudiées et utilisées en technologie CMOS. La première est la structure silicium massif (ou « bulk « ), dans laquelle le transistor est directement fabriqué sur un substrat semiconducteur (figure (1.2.a)). La seconde est appelée SOI (pour l’anglais « Silicon On Insulator ») dans laquelle le transistor est réalisé sur une fine couche de silicium séparée du reste du substrat par une couche d’isolant (figure (1.2.b)). La structure bulk est relativement à la tension de drain et freine la réalisation de CMOS à l’échelle d’un circuit. Afin de retarder l’apparition de ces effets, les technologues disposent de plusieurs paramètres. Un dopage élevé du canal réduit tout d’abord l’épaisseur de la zone de déplétion à une région proche de la grille qui peut alors exercer avec plus d’efficacité son contrôle sur les charges en mouvement. En contre partie le libre parcours moyen des électrons dans le canal diminue et leur mobilité s’en trouve dégradée [8]. Une forte capacité d’oxyde C) facilitedonc la diminution des dimensions. Néanmoins une réduction trop intense de l’épaisseur d’oxyde conduit à des courants de fuite de grille par courant tunnel [9] mettant à défaut la fiabilité. Afin d’atteindre une épaisseur inférieure au nanomètre, l’oxyde de silicium actuellement utilisé devra être remplacé par des matériaux à grande constante diélectrique, notamment par des oxydes binaires de métaux de transition comme le Zr, Hf, Y, et d’autres lanthanides [10].