Avec le phénomène « More Moore » et les tendances « basse puissance », optimiser ou prédire les performances énergétiques des circuits numériques devient de plus en plus difficile. En effet, la variabilité et la difficulté de modéliser précisément le comportement des transistors limitent le bénéfice de la diminution de la taille des transistors. Les méthodologies de conception actuelles prennent en général des marges de conception pour prévenir l’incertitude générée par ces limites et garantir un rendement fonctionnel. Cependant, avec l’ère nanométrique, l’utilisation de marges de conception n’est plus efficace, du fait d’une sur-conception croissante, limitant les optimisations et diminuant le rendement tant paramétrique que fonctionnel.

De nombreuses équipes de recherche travaillent à la mise au point d’outils stochastiques permettant d’évaluer de manière statistique les performances des circuits intégrés. Toutefois, cet axe de recherche, communément appelé Statistical Timing Analysis, ne constitue qu’une des étapes de la mise au point de flots de conception statistique. Une autre étape consiste à mettre au point des méthodes de caractérisation et d’optimisation statistiques permettant de gérer l’énergie d’un circuit tout en permettant de contrôler finement les rendements de fabrication. La mise au point de flots d’évaluation et de conception statistiques devrait permettre au concepteur de définir des variations énergétiques (en fonction de la tension d’alimentation VDD, la tension de polarisation du substrat VBB Voltage Body Biasing, la température, le nombre d’étages…) réalistes permettant d’assurer un fonctionnement correct du circuit au moindre coût.

Pour les nœuds technologiques avancés, le terme « performance » ne signifie plus seulement une fréquence élevée, mais aussi une puissance faible. Il est clair que la réduction de la puissance globale mène à une augmentation du délai. Ainsi, pour estimer l’efficacité globale de l’énergie, il est nécessaire de garantir que pour une certaine fréquence, la puissance consommée est minimale. Avec l’arrivée des technologies CMOS-BULK sub-32nm, les gains en vitesse et en consommation des circuits intégrés, obtenus grâce à la miniaturisation des dispositifs, ne sont plus aussi significatifs qu’ils l’étaient. En effet, certains effets physiques deviennent de moins en moins négligeables et affectent les performances ainsi que la robustesse des circuits. C’est notamment le cas de la consommation statique des circuits qui explose en raison de la forte augmentation des courants de fuite des dispositifs et de leurs dispersions électriques. L’augmentation de la puissance statique dans les nœuds technologiques avancés est due essentiellement aux canaux courts. Les gains en performances se limitent alors à chaque nœud technologique et les courants de fuite des transistors augmentent, ce qui mène à une augmentation non négligeable de la consommation statique. De plus, à chaque nœud technologique, la variabilité de la tension de seuil augmente, ce qui limite la diminution de la tension d’alimentation et empêche par conséquent la diminution de la consommation statique des circuits intégrés.

De plus, pour contrôler la consommation statique dans les nœuds technologiques avancés (en dessous de 32nm), les dispositifs CMOS-BULK conventionnels sont de plus en plus complexes. Le coût de fabrication de ces dispositifs devient lui aussi de plus en plus élevé. De nouvelles architectures de dispositifs sont étudiées pour remplacer les dispositifs CMOS-BULK conventionnels, afin de poursuivre la loi de Moore. Ces dispositifs émergents basés sur des transistors à film de silicium mince non dopé, offrent un meilleur contrôle électrostatique (moins de courants de fuite), améliorent le transport (meilleur mobilité des porteurs) et présentent un canal plus homogène (moins de dispersion). Parmi ces dispositifs, la technologie silicium sur isolant complètement désertée (FDSOI : Fully-Depleted Silicon-On-Insulator) apparait comme une candidate très prometteuse. En outre, par rapport aux autres solutions envisagées (par exemple le FinFET), son architecture planaire proche de celle du BULK est particulièrement avantageuse pour une transition rapide au niveau industriel.

Bien que les avantages de la technologie FDSOI soient maintenant largement démontrés et reconnus au niveau transistor, il est également important d’évaluer les avantages de cette technologie au niveau circuit et plus particulièrement en terme d’énergie. En effet, la réduction de la consommation d’énergie dans les systèmes digitaux est devenue aujourd’hui une préoccupation majeure des concepteurs de circuits intégrés. La réduction de la consommation est l’un des trois paramètres essentiels de la conception, au côté de la vitesse et de l’augmentation de la densité d’intégration. La technologie FDSOI offre des caractéristiques électriques particulièrement intéressantes permettant la conception de circuits intégrés basse tension, basse consommation. Les transistors MOS à film mince de cette technologie offrent un bon contrôle électrostatique de la grille sur le canal, ce qui améliore les effets canaux courts et la pente sous le seuil. Par conséquent, le courant effectif des transistors FDSOI est plus élevé pendant la transition des portes logiques par rapport à celui qui correspond aux transistors MOS sur silicium massif. De plus, les fluctuations au niveau de la tension de seuil sont réduites grâce au film mince non dopé, ce qui permet d’atteindre une tension minimale de fonctionnement des circuits. Ce qui est essentiel pour réduire la consommation.

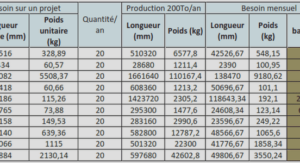

Comme on l’a déjà noté, la puissance statique prend une place de plus en plus importante par rapport à la puissance dynamique dans un circuit. La technologie FDSOI permet de limiter l’impact de cette puissance statique. Dans ce mémoire nous avons donc étudié l’énergie statique de la technologie 28nm FDSOI à partir d’une analyse statistique du délai et la puissance statique. Ces analyses consistent à construire des librairies statistiques du délai et de la puissance statique pour plusieurs valeurs de la tension d’alimentation VDD et pour plusieurs valeurs de la tension de polarisation VBB , ce qui caractérise la technologie 28nm FDSOI. Le délai et la puissance statique des circuits sont alors estimés à partir de cette caractérisation.

L’estimation du délai et de la puissance statique effectuée, l’énergie statique peut être étudiée. Cette énergie étant le produit du délai et de la puissance statique, optimiser l’énergie statique va consister à déterminer le meilleur compromis Délai-Puissance Statique, c’est-à-dire à déterminer une tension d’alimentation optimale et une tension de polarisation optimale qui réduisent le délai sans trop dégrader la puissance statique et vice versa.

Introduction |