Du condensateur élémentaire à la mémoire non volatile qualification de la technologie Fujitsu 0,35 µm

..condensateurs à base de PZT et SBT, ce chapitre traite de la qualification d’une technologie actuellement commercialisée par Fujitsu. Cette étude a été menée dans une approche “bottom-up” en allant du condensateur élémentaire au composant (puce) en passant par des réseaux de condensateurs intégrés. entreprise est actuellement le leader mondial de la technologie en terme de commercialisation avec plus de 150 Millions de composants vendus. Le Tableau (ii) La conservation du matériau PZT jusqu’à une technologie CMOS 90 nm est plus surprenante. En effet, selon Fujitsu, la technologie FeRAM ne nécessite pas l’intégration d’un matériau tel que SBT ou BLT.

L’utilisation d’un matériau à base de bismuth est prévue en 2011 avec l’introduction d’une structure 1T comportant uniquement un transistor. (iii) Concernant, l’architecture du point mémoire, celui-ci conserve une structure 1T/1C jusqu’en 2011 mais l’empilement évolue continuellement. En effet, cette feuille de route programme le passage d’une technologie planaire (pour laquelle le condensateur plan se trouve décalé par rapport au transistor) à une technologie empilée (condensateur plan situé sur le transistor) puis, en 2008, à une technologie 3D empilée. En accord avec le chapitre précédent, ce tableau montre, une fois encore, la nécessité de passer à une technologie 3D.

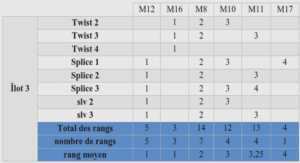

4-1 et possédant une architecture 2T/2C. Ainsi, un wafer intégré (150 mm de diamètre) a été fourni au consortium L2MP/Gemplus pour effectuer des études sur des réseaux de condensateurs intégrés et sur des composants. Pour compléter ces investigations, deux autres wafers possédant des condensateurs élémentaires non intégrés (“short loop”) ont été fournis au L2MP. La 4-2. Ainsi, quatre types d’échantillons (condensateurs élémentaires, condensateurs uniques intégrés, réseaux de condensateurs intégrés et puces) ont été analysés à l’aide de caractérisations électriques et/ou microstructurales: d’hystérésis dynamiques, statiques et des mesures C-V ont été développées.

Elles ont permis de qualifier l’uniformité de la réponse électrique sur l’ensemble du wafer et d’analyser l’influence de sollicitations telles que la tension et la température. (ii) Des premières caractérisations microstructurales ont été menées sur les condensateurs élémentaires et sur les composants. Dans le cas des condensateurs élémentaires, la caractérisation de l’empilement a été effectuée par diffraction des rayons X sur un diffractomètre conventionnel. Les puces ont, quant à elles, été étudiées sur la ligne ID18F à l’ESRF en utilisant un protocole expérimental identique à celui développé pour l’analyse des réseaux de condensateurs 3D de l’IMEC (paragraphe 3.2). Il a donc été possible de caractériser la technologie Fujitsu 2T/2C par microdiffraction et microfluorescence X.

Cependant, la caractérisation microstructurale des échantillons ayant débutée en 2004, il n’a pas été possible de la coupler à des études par microscopie électronique à transmission. Néanmoins, les résultats de microdiffraction et de microfluorescence X ont été comparés à une coupe transverse MET obtenue par Fujitsu.

4-2. Il est important de noter que, afin de qualifier la technologie, les résultats électriques obtenus seront discutés en rapport avec les spécifications couramment utilisées dans l’industrie des mémoires FeRAM. D’autre part, afin de situer cette technologie sur le marché des mémoires FeRAM, les résultats électriques sur réseaux de condensateurs intégrés seront comparés à ceux d’une autre technologie industrielle appelée B dans ce mémoire. études amont sur des condensateurs élémentaires.

Ces investigations permettent de discuter la qualité microstructurale et électrique des condensateurs avant leur intégration dans l’architecture silicium submicronique. cette technologie, le film mince de PZT (de symétrie quadratique), dont l’épaisseur varie de 150 nm pour un wafer à 200 nm pour l’autre, est déposé entre deux électrodes de natures chimiques différentes ce qui peut avoir une influence non négligeable sur la réponse électrique (Scott, 2000 ; Kim & Song, 2003). 4-2-a présente le diagramme de diffraction de rayons X (θ-2θ) obtenu en géométrie Bragg-Brentano sur le domaine angulaire 20-60° en 2θ. La Figure 4-1. En revanche, il n’est pas possible d’indexer toutes les raies car des structures de test inconnues et différentes des condensateurs élémentaires sont également présentes sur la portion de wafer analysée par diffraction.