Conception et étude d’un oscillateur local à commutation rapide

Les performances des systèmes OFDM, comme nous l’avons vu dans le chapitre précédent peuvent être largement améliorées en apportant de la diversité. Le processus de normalisation 802.15.3a [Ieee20031] permet de disposer d’une grande diversité fréquentielle. Ceci est réalisé en envoyant les symboles OFDM sur des bandes de fréquences différentes. Le saut en fréquence, assuré par l’oscillateur local implique de lourdes contraintes sur les caractéristiques de ce dernier. Pour ne pas perdre de débit, le temps de commutation doit être inférieur à 9,47 ns dans le cadre du MultiBands OFDM, ce qui limite l’utilisation des structures classiques d’OL. Dans ce chapitre, nous présentons l’étude d’un synthétiseur de fréquence sur 14 bandes de fréquences de faible complexité à hautes performances pour le standard 802.15.3a, proposé dans [Trav20071]. A partir d’une étude au niveau « système », nous avons réalisé et caractérisé la structure de base sur une filière BiCMOS AMS S35D4. Des résultats de mesure sont ainsi obtenus pour les blocs faisant partie de l’architecture du synthétiseur de fréquences qui ont permis une caractérisation réaliste des performances du système complet. Dans la première partie de ce chapitre nous étudions le cahier des charges du synthétiseur de fréquence ainsi que les possibilités de réaliser un tel système. Nous présentons les contraintes pour réaliser un tel Oscillateur Local (OL) à l’aide de structures classiques. Une comparaison est faite sur les avantages et les inconvénients des synthétiseurs agiles déjà proposés dans la littérature suivie par la présentation du synthétiseur de fréquence sur lequel nous concentrons notre étude.

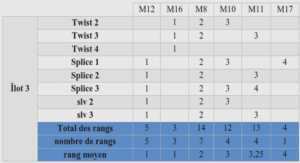

La deuxième partie est consacrée à la conception de chaque bloc faisant partie de l’OL étudié. Nous étudions la technologie microélectronique disponible, le type et les solutions schématiques appropriés pour les mélangeurs, les diviseurs, les multiplexeurs et les filtres utilisés. Nous réalisons la conception du layout en insistant sur les bonnes pratiques pour éviter le déséquilibre de phase et d’amplitude entre les voies. Les performances attendues sont montrées par des simulations post-layout. Après avoir conçu les blocs nécessaires ainsi que la structure de base du synthétiseur de fréquence, nous effectuons les mesures des circuits réalisés. L’équipement de mesure ainsi que les bancs de test sont présentés. Les résultats obtenus sont commentés et comparés aux résultats de simulation. Pour le processus de normalisation 802.15.3a, appelé aussi MultiBands OFDM, l’émission des symboles peut être effectuée autour de 14 fréquences centrales [Ieee20031]. Chaque bande allouée répond aux critères de « Ultra-Wideband » [Fccr2002] et présente une largeur de 528MHz. Les 14 bandes forment 4 groupes de 3 bandes chacune – mode de 1 à 4 et 1 groupe de 2 bandes – mode 5. Le plan de fréquence est présenté sur la figure Figure II-1.

Etant une technologie « grand public », le MultiBands OFDM implique des contraintes très exigeantes au niveau de l’intégrabilité, de la taille, de la consommation et du coût du transmetteur complet. Par conséquent, pour le récepteur et l’émetteur, c’est l’architecture à transposition directe (homodyne) qui s’impose en répondant au mieux à ces contraintes. Dans cette configuration, l’Oscillateur Local (OL) doit donc avoir la fonction de générer directement les fréquences centrales de toutes les 14 bandes fournissant le signal par deux voies déphasées en quadrature, nécessaires pour les modulateurs et les démodulateurs I/Q. L’architecture la plus intuitive pour créer un oscillateur local à fréquence variable est celle utilisant une seule boucle à verrouillage de phase PLL (Phase Locked Loop), Figure II-2. Le changement de la fréquence est assuré par le diviseur, dans sa boucle de retour à facteur de division « N » programmable. La difficulté principale de la réalisation d’un tel synthétiseur de fréquences est le temps de commutation. Bien que ça soit une solution très flexible au niveau de la plage de fréquences générées, sa rapidité de commutation est directement liée à fréquence de référence (fREF).

En effet, le temps nécessaire pour que le régime établi soit atteint après avoir effectué un saut en fréquence est de l’ordre de 100 cycles de la fREF [Lee2005]. Les synthétiseurs numériques DDS (Direct Digital Synthesizer) permettent une grande souplesse et rapidité en formant le signal généré. Le signal de sortie est obtenu par des convertisseurs CNA. Leur utilisation pour des fréquences supérieures à quelques GHz est limitée par la consommation et le coût élevés [Vank2000]. De plus, vu la largeur de la bande nécessaire pour une application MB-OFDM entre 3,1GHz et 10,6GHz, le filtre à la sortie du CNA nécessite d’être accordable, tout en respectant le temps d’établissement au-dessous de 9.47ns.