Au cours des dix dernières années, les systèmes embarqués ont connu un développement fulgurant au point qu’ils font aujourd’hui parti de notre vie quotidienne: téléphones portables, tablettes numériques, ordinateurs de bord, assistance médicale… Les applications ayant recours à ce type de systèmes sont nombreuses et ont besoin de toujours plus de puissance de calcul. Les circuits développés sont également de plus en plus complets et tendent à embarquer un système complet composé d’un ou plusieurs processeurs, de mémoire, et éventuellement d’accélérateurs matériels. On parle alors de système sur puce (en anglais System-on-Chip, SoC) .

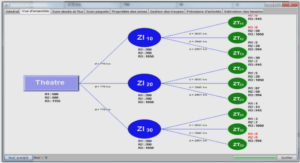

En particulier, le calcul reconfigurable a connu un essor considérable, faisant du FPGA (Field Programmable Gate Array) un composant essentiel des systèmes embarqués. En effet, le FPGA offre un bon compromis entre une solution logicielle, flexible et lente à cause de son exécution temporelle, et une solution matérielle à base d’ASIC (Application Specific Integrated Circuit, un circuit intégré spécialisé), très rapide grâce à une exécution spatiale et parallèle mais peu flexible . Malgré un coût en grande série très supérieur à celui de son équivalent ASIC, un système basé sur un FPGA aura toutefois un temps de mise sur le marché bien inférieur, ce qui en fait un parfait candidat pour le prototypage rapide. Lorsqu’un système complet est implanté sur un composant programmable, on parle alors de système sur puce reprogrammable, ou en anglais SoPC (System on Programmable Chip). Toutefois, les FPGA classiques ne peuvent pas modifier leur comportement en cours d’exécution. Prenons l’exemple d’un système composé d’un accélérateur matériel disponible en trois versions plus ou moins efficaces qui sont activées individuellement selon les performances requises par le système. Même si un seul accélérateur est actif à la fois, les trois doivent être présents sur le FPGA à tout instant. Partant de ce constat, Xilinx a développé le concept de reconfiguration dynamique partielle (dans le manuscrit, nous utiliserons indifféremment le terme reconfiguration dynamique).

Introduite à la fin des années 1990 avec la série de FPGA XC6200, la reconfiguration dynamique permet la modification d’une partie prédéfinie du FPGA pendant que le reste du design s’exécute normalement. Ainsi, il est possible de changer les fonctionnalités du système en cours d’exécution, permettant de réduire la surface nécessaire et/ou la consommation d’énergie du FPGA [17, 18]. En reprenant l’exemple précédent, il serait alors possible de n’avoir qu’un seul accélérateur instancié sur le FPGA à chaque instant. En dépit de caractéristiques intéressantes, la reconfiguration dynamique reste n’est toujours pas ancrée dans l’industrie [19]. Nous y voyons deux raisons principales. La première raison est un problème de performances pour la reconfiguration dynamique. En effet, le contrôleur de reconfiguration fourni par Xilinx ne permet pas d’atteindre des débits intéressants. Si l’on considère que le système doit ordonnancer des tâches matérielles, le temps de reconfiguration est crucial et si celui-ci est trop grand devant le temps d’exécution de la tâche au point d’en devenir inacceptable, le concepteur privilégiera une solution statique classique [20, 21].

La seconde raison de l’absence de la reconfiguration dynamique dans l’industrie aujourd’hui est selon nous la difficulté de conception de telles architectures. Tout d’abord, il est impossible de simuler un système avec des outils classiques comme par exemple ModelSim, qui ne permet pas de modifier les modules en cours de simulation. La validation s’effectue donc directement sur carte, pendant la dernière phase du processus de conception : l’implémentation. L’identification d’un problème lors des dernières phases de conception d’un système est très coûteuse, notamment en temps de développement pour le résoudre. C’est pour cela que durant ces dernières années, la tendance est à l’élévation du niveau d’abstraction lors de la conception afin d’identifier de potentiels problèmes au plus tôt dans le cycle de développement. Enfin, la définition de l’architecture du système reconfigurable est un problème très vaste qu’il faut aujourd’hui résoudre en explorant manuellement l’espace de conception, qui grandit exponentiellement avec le nombre de tâches considérées. Pour ces raisons, la reconfiguration dynamique des FPGA reste un thème de recherche majeur qu’il est compliqué d’intégrer à une approche industrielle de la conception de systèmes. Le projet ARDMAHN (Architectures Reconfigurables Dynamiquement pour l’Auto-adaptation en Home Networking) [22], financé par l’Agence Nationale de la Recherche (ANR) a pour objectif de répondre à cette problématique.

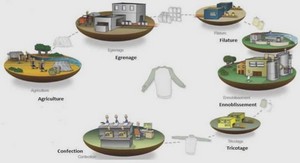

Ce projet se place dans le contexte des applications multimédia qui prennent une part importante dans le quotidien des utilisateurs, notamment pour la diffusion de flux. Mais, avec l’explosion des terminaux et des types de réseaux d’accès, l’hétérogénéité devient aussi omniprésente. Malheureusement, pour le moment, les éléments de la chaîne de distribution de services multimédia n’intègrent pas cette nouvelle contrainte. La gestion et le traitement du flux multimédia doivent être réalisés tout au long de la chaîne de distribution : de sa génération dans les « Têtes de réseaux », pendant son acheminement à travers les réseaux de distribution et jusqu’aux utilisateurs finaux. L’adaptation dynamique et transparente de ce flux multimédia selon les caractéristiques du ou des consommateurs demandeurs et de leur(s) environnement(s) (hétérogènes) est la clé du succès des services réseaux de demain.

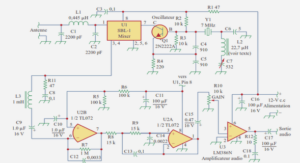

L’adaptation d’un flux multimédia aux caractéristiques des réseaux de distribution et aux besoins de l’utilisateur est un processus complexe demandant d’importantes ressources de calcul. Cette adaptation repose sur des techniques de transcodage, transrating, transizing, ajout de données, etc. La complexité de ces techniques, d’une part, et les contraintes sur les temps de réponses, d’autre part, génèrent des problèmes d’implémentation, d’intégration et de validation très difficiles à maîtriser. Une nouvelle approche des phases de définition, spécification et implémentation s’impose. Dans ce projet, nous résoudrons ces problèmes de performances et de timing en transférant une partie des fonctions d’adaptation du domaine logiciel vers le domaine matériel, principalement via des technologies de type FPGA.

Dans ce domaine, si l’adaptabilité à des évènements connus peut être maîtrisée sur des fonctions purement logicielles, elle est quasi inexistante sur des fonctions matérielles. Or, les architectures matérielles auto-adaptatives sont un enjeu essentiel pour les prochaines générations d’équipements de diffusion et d’exploitation de services. En effet, la vitesse d’exécution des fonctions et l’énergie consommée sont deux facteurs particulièrement limitant et de surcroît antagonistes dans les applications embarquées. Le coût et l’encombrement du système de refroidissement sont parfois un obstacle aux développements. Bien gérée, la reconfiguration dynamique peut permettre d’allier performances, faible consommation et adaptabilité en utilisant les technologies récentes. Même si elle est perfectible, la technologie est disponible, en revanche la mise en œuvre optimale, sa vérification et validation architecturale restent à imaginer.

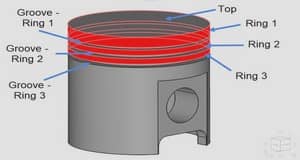

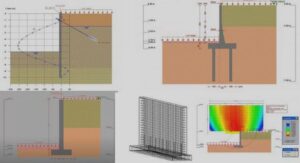

1.1 Comparaison des approches pour les systèmes embarqués |