Les types de CMOS utilisés pour les capteurs d’images

La technologie CMOS (Complementary Metal Oxide Semiconductor) est un assemblage technologique permettant de réaliser sur un même substrat des transistors NMOS et PMOS. Cependant il existe plusieurs types de technologies CMOS et parmi les plus connues, on peut citer trois qui sont utilisées pour les capteurs d’images : La technologie CMOS à caisson n, La technologie CMOS à caisson p, Et la technologie CMOS à double caisson.

Une technologie CMOS à caisson n utilise un substrat en silicium de type p dans lequel est formé un caisson en silicium de type n. Des transistors PMOS sont alors réalisés dans ce caisson et des transistors NMOS dans le substrat .

Une technologie CMOS à caisson p : le substrat en silicium de type n contient un caisson en silicium de type p. Les transistors NMOS sont situés dans le caisson alors que les PMOS se trouvent dans le substrat.

Et afin la technologie CMOS à double caisson, le substrat en silicium est de type quelconque et dans lequel on a des caissons de type p et de type n .

Architecture des CMOS

La technologie CMOS utilise à la fois deux types de transistors (NMOS et PMOS). Ces deux transistors fonctionnent de façon inverse (quand l’un est passant, l’autre est bloquant) d’ où le nom Complementary. Les circuits électroniques en technologie CMOS sont construits de façon que tous les NMOS sont soit reliés à la masse, soit à un autre transistor de type NMOS. De même tous les PMOS sont soit reliés à la tension d’alimentation, soit à un autre PMOS.

La composition d’un transistor PMOS crée une faible résistance entre ses contacts de source et de drain quand une tension de grille basse est appliquée et une résistance élevée lorsqu’une tension de grille élevée est appliquée. D’autre part, la composition d’un transistor NMOS crée une résistance élevée entre la source et le drain lorsqu’une tension de grille basse est appliquée et une faible résistance lorsqu’une tension de grille élevée est appliquée. CMOS réalise la réduction de courant en complétant chaque NMOS avec un PMOS et reliant les deux portes et les deux drains ensemble. Une haute tension sur les grilles entraînera le NMOS à conduire et le PMOS à ne pas conduire, tandis qu’une basse tension sur les portes provoque l’inverse. Cet arrangement réduit considérablement la consommation d’énergie et la production de chaleur.

Cependant, pendant le temps de commutation, les deux MOS conduisent brièvement lorsque la tension de grille passe d’un état à un autre. Cela induit une brève augmentation de la consommation d’énergie et devient un problème grave à des fréquences élevées .

Fabrication des CMOS

La fabrication des CMOS commence avec une tranche (wafer) en silicium. La technologie utilisée pour implanter les composants électroniques sur le wafer est la VLSI (Very Large Scale Integration) qui consiste à créer couche après couche les structure élémentaires du circuit.

La photolithographie (définition des zones actives gravure et remplissage)

Elle permet la construction des chemins pour les électrons et les barrières isolantes pour les séparer . Les étapes suivantes sont nécessaires pour l’application complète du procédé de la photolithographie.

Oxydation : pour cette étape, on dépose une mince couche de SiO2 (dioxyde de silicium) sur la tranche au complet, en l’exposant à un mélange d’oxygène et d’hydrogène à environ 1000°C. L’oxyde est utilisé comme isolant et pour créer la grille des transistors.

Résine photosensible : elle permet de protéger certaines parties du circuit pendant la création de certains niveaux. La résine photosensible (polymère) sensible à la lumière est répandue uniformément sur toute la surface du support. Ce matériel est sensible aux solvants organiques, mais durci et devient insoluble lorsqu’il est exposé à de la lumière UV. Ce type de résine est une résine négative. Mais cependant la résine positive a la propriété inverse : elle est originalement insoluble, mais devient soluble lorsque exposée à de la lumière UV.

Exposition UV : un masque qui contient les motifs à transmettre est placé à proximité de la tranche. Le masque est opaque aux endroits qu’on ne veut pas modifier et transparent aux autres endroits. La combinaison de masque et de la tranche est alors exposée aux rayons UV, ce qui entraine la solubilité des parties de la tranche où le masque est transparent.

Finition : on place ensuite les tranches dans un acide ou une base pour enlever le SiO2 mis à nu. La tranche est ensuite ‘‘cuite’’ à basse température pour durcir encore la résine.

Gravure acide : du matériel est enlevé de la tranche des parties non couverte par la résine. Différentes acides et bases sont utilisés selon le matériau à enlever.

Nettoyage : on nettoie la tranche avec de l’eau sans ions et on la sèche avec de l’azote. A cette étape, il est nécessaire d’éliminer au maximum les particules de poussière dans la pièce. Cette étape est effectuée dans des chambres spéciales.

Diffusion et implantation d’ions

La diffusion et l’implantation d’ions représentent les deux méthodes principales de faire le dopage. La diffusion consiste à placer les tranches dans un tube de quartz. Et ces tranches vont être chauffées à l’intérieur de ce dernier. Un gaz contenant le dopant est ensuit introduit dans le tube. Les dopants vont donc se diffuser dans les parties exposées à cause des températures élevées. Avec l’implantation d’ions, un faisceau d’ions balaie la surface et les ions vont pénétrer dans le matériau exposé. La profondeur d’implantation et la concentration sont déterminées respectivement par l’accélération des ions et le temps d’exposition. Les défauts liés au déplacement d’atomes dans le substrat peuvent être corrigés en chauffant la tranche à 1000°C pendant au moins un quart d’heures . Ce déplacement d’atomes dans le substrat est causé par la collision entre les ions et les atomes du matériau. L’implantation d’ions remplace de plus à plus la diffusion du fait qu’elle permet un contrôle plus précis.

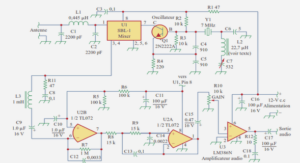

Amplificateur colonne

L’amplificateur colonne appelé aussi circuit de colonne permet de recueillir, stocker et amplifier l’information issue du pixel. Dans un capteur d’images standard, il y a un amplificateur colonne par colonne de pixels (ce qui justifie son appellation). Tous les amplificateurs reçoivent en même temps les signaux provenant de la ligne active de l’imageur. Ces signaux seront échantillonnés puis stocker par l’ensemble des circuits de lecture colonne. Par la suite, un parcours séquentiel des amplificateurs colonne permettra de fournir les signaux amplifiés au convertisseur analogique numérique.

En effet l’amplificateur colonne prend comme modèle des architectures des circuits comparateurs rapides couramment utilisés pour la réalisation des convertisseurs analogiques numériques . Son fonctionnement est semblable à celui d’une bascule D. Le signal de commande Latch joue le rôle de l’horloge, l’entrée D est constituée par la différence de tensions présentes en A et B enfin la sortie de cette bascule soit Sout.

Table des matières

Introduction générale

Chapitre I : Architecture et fabrication des circuits CMOS

I-1 Introduction

I-2 Les types de CMOS utilisés pour les capteurs d’images

I-3 Architecture des CMOS

I-4 Fabrication des CMOS

I-4-1 La photolithographie (définition des zones actives gravure et remplissage)

I-4-2 Diffusion et implantation d’ions

I-4-3 Dépôt de la couche de passivation

I-4-4 Création des contacts métalliques

I-5 Conclusion

Chapitre II : Présentation des capteurs d’images CMOS

II-1 Introduction

II-2 Architecture des capteurs d’images CMOS

II-2-1 La matrice d’éléments photosensibles

II-2-1-1 Le photodétecteur (photodiode)

II-2-1-2 La mémoire SRAM

II-2-2 Les pixels

II-2-2-1 Les pixels à intégration

II-2-2-2 Les pixels à fonctionnement continu

II-2-3 Amplificateur colonne

II-2-4 Le décodeur de ligne

II-3 Conclusion

Chapitre III : Caractéristiques et performances des capteurs d’images CMOS

III-1 Introduction

III-2 Caractéristiques

III-2-1 Paramètres géométriques

III-2-1-1 La résolution

III-2-1-2 La taille des pixels

III-2-1-3 Le facteur de remplissage

III-2-2 Paramètres électriques et physiques

III-2-2-1 Le rendement quantique

III-2-2-2 Le courant d’obscurité

III-2-3 Bruits des imageurs CMOS

III-2-3-1 Bruit temporel

III-2-3-2 Bruit spatial fixe (BSF)

III-3 Les performances

III-3-1 La dynamique de fonctionnement

III-3-2 La vitesse de lecture

III-4 Conclusion

Conclusion générale

Bibliographie