Développement d’architectures 3D à base de transistors MOS à canal nanofil III-V

Stratégie verticale pour un dispositif 3D

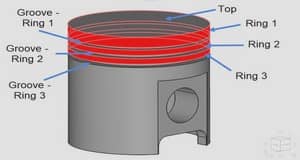

Pour utiliser une grille entourant totalement le canal, la structure la plus naturelle est le nanofil cylindrique. En effet, le champ électrique agira de manière symétrique pour la formation du canal contrairement à une structure parallélépipédique telle qu’un nanoruban qui possèdera des effets de conduction de coin. Les simulations proposées par Ansari et al. [18] prédisent que les nanofils sont les nanostructures permettant d’obtenir un fonctionnement transistor jusqu’à une longueur de grille de 3 nm. Pour l’utilisation de nanofil, deux intégrations sont envisageables : des nanofils horizontaux ou verticaux.

Architecture horizontale

Différentes stratégies d’intégration ont été démontrées pour l’obtention de transistors à base de nanofils horizontaux. Les nanofils peuvent être réalisés selon un procédé de croissance tel que VapeurLiquide-Solide (VLS) en utilisant des billes métalliques comme catalyseurs et guides de croissance. Les nanostructures obtenues sont ensuite transférées sur un substrat Si sur lequel le transistor 17 sera réalisé (Figure I-9a). Afin d’obtenir une grille totalement entourante, les nanofils horizontaux sont nécessairement suspendus pour permettre l’intégration de la grille sous celui-ci (Figure I-9b) [23]. Figure I-9 : a) FET tri-grilles à base d’un nanofil de Si horizontal. [22] b) FET à base d’un nanofil de Si suspendu dont la grille totalement entourante est formée par oxydation thermique. [23] La voie par croissance utilise des procédés peu adaptés à l’intégration grande échelle : utilisation de catalyseur Au contaminant les transistors et transfert des nanofils par dispersion dans un fluide ne permettant pas un positionnement précis. Ce type d’architecture a également été réalisé par gravure du Si. Cela a, par exemple, était réalisé à l’aide d’une oxydation sacrificielle [24]–[27]. La première étape est l’obtention d’une ailette en Si par un enchaînement de photolithographie et de gravure plasma. Une fois cette ailette obtenue, une oxydation suivie de l’élimination de l’oxyde permet d’obtenir les nanofils horizontaux suspendus. Un procédé utilisant également une couche sacrificielle a également été mis au point par la société Samsung [28]. Le procédé commence par la création d’empilement Si/SiGe par épitaxie puis à la définition d’une ailette par les techniques classiques de microfabrication. La gravure sélective isotrope du SiGe permet alors de libérer les nanofils de Si [29], [30]. Chacune des couches de silicium en sandwich entre deux couches de SiGe permettra alors d’obtenir des nanofils distincts superposés (Figure I-10). Cela est un moyen d’augmenter la densité d’intégration en empilant les canaux de conductions plutôt que de les distribuer sur la surface. 18 Figure I-10 : Images MEB de transistors à nanofil de Si horizontaux réalisés par gravure. a) Fils suspendus alignés parallèlement [25]. b) Empilement de nanofil suspendus [30]. Insert : observation TEM d’une coupe radiale de ces nanofils [31]. Les transistors à base de nanofils horizontaux ont été étudiés majoritairement lors de la décennie 2000 – 2010. Les procédés de fabrication proches des approches planaires ne perturbent pas la philosophie d’intégration. D’un autre côté, l’utilisation d’une architecture verticale présente plusieurs avantages bien que le défi technologique soit nettement plus ardu.

Architecture verticale

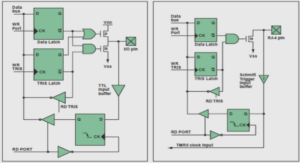

L’obtention de transistors avec une architecture verticale a été moins étudiée car l’intégration 3D représente une rupture majeure avec les architectures conventionnelles. Le tout premier dispositif vertical a été proposé en 1988 par Takato et al. [32], [33] où un piller de Si de 1 µm de diamètre est obtenu par gravure. Des caissons de dopants ont été implantés au sommet et au pied du pilier pour réaliser un fonctionnement transistor classique. Ce dopage a pu être réalisé grâce à la résolution des techniques de microfabrication contemporaine permettant d’obtenir un pilier d’au minimum 1 µm de diamètre. Une telle implantation de dopants n’est pas possible sur des nanostructures dont les diamètres atteignent aujourd’hui quelques dizaines de nanomètres. Des dispositifs à nanofil verticaux ont été obtenus par croissance sur Si(111) [34], [35] présentant un diamètre de 40 nm à 20 nm pour des hauteurs s’élevant de 400 m à 1 µm. La croissance verticale est de nouveau dirigée par un catalyseur d’or qui est conservé au sommet. La fabrication du transistor suit ensuite des étapes classiques de microfabrication (photolithographie, gravure sèche et humide, métallisation), à l’exception que, les couches étant empilées les unes sur les autres, il est nécessaire d’isoler électriquement grille, source et drain. Ce rôle est tenu par l’oxyde de grille en SiO2 qui est utilisé comme espaceur (Figure I-11).

Introduction |