Contribution à l’intégration 3D de composants passifs pour l’électronique de puissance

The application target: decoupling of DC-to-DC power converters

All power electronics converter topologies are based on the association of switching cells using power switches from 2 to 2n (two-levels to n+1 levels). In most cases, the switching cells are connected to a DC-to-DC bus. In all cases, the switching cell requires adding decoupling capacitors on the DC bus, as close as possible to the power switches, in order to minimize parasitic inductance of the physical switching loop and therefore to minimize the turn-off overvoltage. Therefore, decoupling is a very demonstrative function to apply the « capacitor-integrated-in-substrate » concept and to validate corresponding technologies.

Two examples requiring planar integrated decoupling capacitor

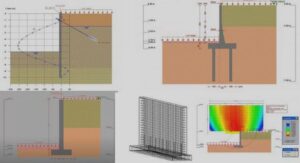

Two particular examples to emphasize the interest in designing planar integrated capacitors have been selected. On one hand, the proposed approach can be used to integrating the plane’s capacitive zones in available areas in existing devices, and, on the other hand, it aims to take advantage of plane configuration to obtain three-dimensional devices by stacking elementary plane switching cells. In both cases, the vicinity between decoupling capacitors and power switches is a critical feature. Figure 1.8 illustrates these two possible application approaches: (a) (b) Figure 1.8: Projection of capacitor integration: (a) Decoupling in the power module, (b) Decoupling in a multi-cell converter. Figure 1.8(a) presents an example of the first option. The surface available inside a power module could be used to integrate a decoupling capacitor directly in the module, above the semiconductor devices. Gate drivers could be moved to the top face. If the capacitor is thin enough, the height of the module can remain unchanged, thereby creating an improved technological cell that includes the decoupling and the gate drivers. With the expected thickness of the capacitive layers being around few hundred of µm, this target appears to be reachable. The electrodes shown in the schematic representation of Figure 1.8(b) are not representative, due to the exploded view of the capacitive zone, and connection parts are not represented. To make possible the proposed concept in order to constitute a completely integrated switching cell, many critical issues still have to be solved: – Interconnection of the upper face of the die. – Interconnection of the plane capacitor with the previous part. – Creation of conductive vias through the capacitive zone to connect the gate driver to the dies. The second option concerns parallel multi-cell converter topologies. The elementary cell should be implemented on a capacitive plane substrate and n samples of this elementary block should be stacked to constitute an n-cell converter. As in the previous case, critical issues must be solved in the same manner, namely: interconnections between the stacked cells and thermal management of the dies. Therefore, the aim of the present work is to implement capacitive substrates on significant areas (a few cm²) and to obtain high specific capacitance values with a low number of layers by using high-permittivity materials. The issues concerning interconnection and thermal management are not considered here. Nevertheless, it was necessary to validate the proposed technology in a configuration that includes semiconductor power devices

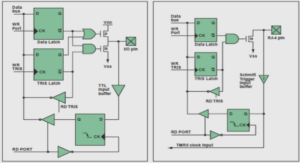

First demonstrator: classical decoupling function on DC bus

The first demonstrator is made with the well-known and basic, two-level switching cell that can be achieved with nearly any kind of power device (Figure 1.9, only MOSFET or IGBT+diode options are considered here). This part of the present work focuses mainly on this decoupling capacitive function. Additional capacitors can be introduced on the DC bus as a part of a common mode filter, if necessary. Both capacitive functions, decoupling and common mode filtering, are considered in the final demonstrator. The capacitor value needed to achieve the decoupling function correctly in that cell can be estimated by using the following equation (1).Capacitance value for decoupling. With: – P = Vin.Ion nominal output power of the cell in DC conversion mode – Fsw, switching frequency – DVin/Vin relative voltage ripple across the decoupling capacitor, maximal value obtained for a duty-cycle D = 0.5 and Io = Ion For common mode filtering, capacitor’s values are approximately five to ten times lower than the decoupling ones. The substrate designed for this first demonstration and the complete cell are presented in the fourth and fifth sections of this dissertation respectively. The proposed commutation cell is expected to operate with the following characteristics: P = 2000W, Vin = 200V, Ion = 10A, Fsw = 100kHz This choice induces significant values for the decoupling capacitor: around one to two µF for a relative voltage ripple of 10% (see Figure 1.10).

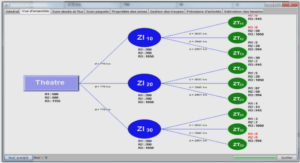

Second demonstrator: decoupling function in flying capacitor converters

The second demonstrator is based on a more specific converter, the multi-level flying capacitor converter, considered for designing Point-of-load (POL) DC-DC converters. POL converters are used in a wide range of applications, from portable devices, electric vehicles, and automotive control to renewable energy applications. These applications continuously demand higher power density, higher conversion efficiency converters with smaller size, lighter weight, and lower cost. Innovative active and passive integration technologies are key factors for obtaining higher efficiency and greater levels of integration. Challenges for obtaining higher power density in POL converter integration include : – Minimization of switching losses in order to increase both efficiency and switching frequencies. – Integration of both active semiconductors and passive components while minimizing parasitic capacitors and inductors. Therefore, an option to overcome the above issues is the series multilevel topology presented in Figure 1.11. The series association of low-voltage semiconductor devices is very efficient in switching operation and the topology allows reducing output filter size. In that converter, the flying capacitors perform again a decoupling function but the total capacitive energy stored is higher than in a classical two-level cell. Therefore, it is also a good option to demonstrate the interest of integrated capacitors in such a structure.

AcknowledgementsI |