Synthèse d’architectures de circuits FPGA tolérants aux défauts

Les Field Programmable

Gate Arrays (FPGAs) ont été développés depuis 15. Grâce à l’évolution technologique ces circuits n’ont cessé de se développer et de nombreux fabricants se sont depuis lancés dans la fabrication de FPGAs (Xilinx, Altera, Actel…). Portant de l’évolution technologique, un FPGA peut maintenant contenir plusieurs millions de portes logiques [51]. Ces circuits sont composés d’éléments logiques interconnectés entre eux par des ressources de routage. La particularité d’un FPGA vient de sa reconfigurabilité. Les éléments logiques ainsi que le réseau d’interconnexion peuvent être reconfigurés dans le but de supporter une autre application. En effet, les FPGAs sont composés de blocs mémoire qui permettent de configurer et de gérer la fonctionnalité du circuit. Il existe plusieurs types de FPGA (les SRAM-based FPGA, les Flash-based FPGA et les Antifuse-based FPGAs), classés en fonction de la manière dont ils sont programmés. La majorité des FPGAs utilisent des mémoires statiques (Fig 2.1) et sont appelés SRAM-based FPGA. La configuration du FPGA est chargée dans une mémoire statique. La cellule a besoin d’être activée pour pouvoir charger la configuration. Ce type de mémoire peut être configuré via une source externe comme une mémoire ash ou via un processeur. Les FPGAs du commerce fabriqués par Xilinx et Altera utilisent ce type de configuration. Les Flash-based FPGA quant à eux ne sont pas équipés de mémoire statique et gardent leur configuration même quand ils ne sont pas alimentés. Le principal avantage de cette technologie est qu’elle consomme moins et est aussi tolérante aux radiations, c’est pourquoi elle est principalement utilisée dans le domaine médical. Enn, les Antifuse-based FPGAs sont composés d’une série de fusibles et sont principalement utilisés dans le domaine spatial. Ces fusibles sont brûlés lors de la configuration du FPGA. Il n’est donc pas possible de le reprogrammer. Cependant, tout comme les Flash-based FPGA ils consomment moins que ceux équipés d’une mémoire statique (SRAM-based). Pour nir, les SRAM-based FPGA sont les FPGA les plus répandus, c’est pourquoi nous avons choisi de développer un FPGA composé de ce type de mémoire. 2.1 Les différentes architectures des FPGAs Un FPGA est composé d’une matrice d’éléments logiques appelés Configurable Logic Block (CLB) connectés entre eux par des ressources d’interconnexions (Fig 2.2).Chaque CLUB est composé de BLÉs (Basic Logic Element) utilisés pour implémenter la partie logique du circuit. Un CLB est donc caractérisé par le nombre de ses entrées I et par le nombre N de BLÉ qu’il contient. Dans les FPGAs modernes ce nombre de BLÉ peut varier de 3 à 12 et chaque BLE peut être connecté à n’importe quelle entrée I du CLB ou à un autre BLÉ comme indiqué par la guerre 2.3.a). Un BLÉ est composé d’un ensemble de tables de transcodage (Look Up Table : (LUT) en anglais) ainsi que d’une bascule D pour implémenter les fonctions de bases grâce au bloc mémoire (SRAM), suivie d’un multiplexeur. Un BLÉ est composé de k Look Up Table ce qui permet d’implémenter une fonction logique à k entrées et une sortie et nécessite 2 k blocs mémoire pour la configuration. La bascule D quant à elle permet de choisir entre un fonctionnement logique ou séquentiel. Ensemble les LUT et la bascule D forme un Basic Logic Element (BLE illustré gure 2.3.b)). Des études ont montré que la meilleure architecture de LUT en termes de performances est une LUT ayant 4 entrées [60] [2]. Les éléments logiques sont connectés entre eux et aux entrées/sorties grâce au réseau d’interconnexion. Ce réseau est programmé de la même manière que les éléments logiques avec des RAMs statiques. L’ensemble permet de configurer complètement le FPGA. En théorie, il est donc possible de charger n’importe quelle fonction logique sur un FPGA. Enfin, la reprogrammation de l’ensemble des SRAM permet de reconfigurer entièrement le circuit et donc de changer l’application ou la fonction du FPGA. Pour nuire, lors de la configuration du FPGA, la netlist contenant l’ensemble des connexions est envoyée au FPGA. Le placement des blocs logiques et la manière dont ils sont interconnectés est alors défini par un algorithme de placement et de routage.

FPGA matriciel (Mesh)

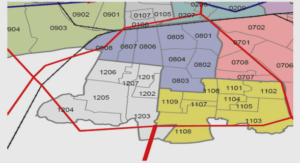

L’architecture la plus répandue et utilisée dans le commerce est l’architecture matricielle (Mesh) [10] [11] [18] [69] [34] [59] appelée aussi architecture de type îlot (Island style). Elle est composée d’une matrice de tuiles en deux dimensions, chaque tuile étant composée d’éléments logiques (CLB) et de ressources d’interconnexions avec des blocs de Connexions (C) et des Switch boxes (S comme indiqué sur la gure 2.4). Les blocs de connexions C sont utilisés pour connecter les éléments logiques au réseau d’interconnexion tandis que les Switchs boxes permettent de connecter l’ensemble des blocs de connexions C. Ce réseau d’interconnexion en 2 dimensions organisé en lignes et en colonnes est distribué tout autour des éléments logiques et permet de connecter n’importe quels éléments logiques entre eux ou aux entrées/sorties du FPGA. Le nombre de connexions (CW) entre les Switch boxes et les blocs de connexions représente le canal de routage (CR) du FPGA. Ces blocs d’interconnexions diffèrent par leurs topologies et leur exigibilité. Pour les blocs de connexions (C), la flexibilité est définie par le nombre de routages du bloc d’interconnexions auxquels les entrées/sorties d’un bloc logique peuvent être connectées. Elle peut donc être définie par deux paramètres Ficin et Coût (Fci N représente le nombre de connexions entre le bloc d’interconnexions et les entrées du bloc logique et Coût entre le bloc d’interconnexions et les sorties du bloc logique). Par exemple, dans la guerre 2.5.a), chaque CLB peut être connecté à deux slots du bloc de Connexions (C), la exigibilité sera donc Fin = Scout = 2. Les Switchs boxes utilisées pour interconnecter les blocs de Connexions au canal de routage (CR) ont plusieurs topologies. En eet, il existe des Switchs boxes avec une topologie appelée disjoint [32], ou wilton [70] et pour nuir universel [20]. La topologie va définir le nombre de connexions entre le canal de routage et chaque entrée d’un même bloc de Connexions (C). Ce nombre permet de définir la flexibilité des Switch boxes Fs. Par exemple, dans la guerre 2.5.b), chaque segment en pointillés représente une connexion possible. Il y a 3 connexions possibles, La flexibilité est donc Fs = 3. Le canal de routage est formé de rails de routage permettant de connecter les blocs Connexions et les Switch boxes. Le nombre de lits du canal de routage CW est appelé largeur (ou taille) du canal. Cette taille est la même pour toute l’architecture du FPGA. La taille du canal de routage doit être fixée avant la fabrication du FPGA par le concepteur car c’est l’un des paramètres architecturaux les plus importants dans l’architecture d’un FPGA. En eet, le canal de routage doit permettre de router l’ensemble des signaux de l’application utilisée par le FPGA sinon on dit que l’application est non routable. Un canal de routage contient des lacs de différentes longueurs. Cette longueur dépend du nombre de blocs logiques longeant le l en question. La gure 2.6 montre un canal de routage avec des longueurs allant de 1 à 4. Pour une longueur de la supérieure à 1, le nombre de commutateurs programmables (switchs) traversés est réduit cela permet donc de réduire la surface ainsi que le délai de routage. Cependant, cette solution diminue la flexibilité du FPGA donc augmente la di culté de routage de l’application. Dans l’industrie, les FPGAs sont souvent composés de segments de routage de différentes longueurs.

FPGA arborescent (Tree)

Pour réduire l’influence du réseau d’interconnexion et se rapprocher des performances en termes de surface et de vitesse des ASICs, une deuxième architecture de FPGA a été développée appelée Tree-based FPGA [1] [19] [43] [26] [50] [49]. En et dans les mesh, 90% de la surface est occupée par le réseau d’interconnexions et le nombre important de commutateurs traversés augmente considérablement le délai de propagation. Une réduction du nombre de commutateurs dans l’architecture devrait donc permettre d’améliorer les performances du FPGA. Dans l’architecture arborescente (Tree), les blocs logiques sont regroupés sous forme de clusters et chaque cluster est composé d’un réseau local d’interconnexion sous forme d’une Switch box (illustré gure 2.7). Une Switch box est composée d’un réseau descendant pour connecter les entrées du cluster aux blocs logiques appelé Downward Mini Switch box (DMSB) ainsi que d’un réseau montant pour connecter les éléments logiques aux sorties du cluster appelé Upward Mini Switch box (UMSB). Pour connecter les UMSB/DMSB aux blocs logiques une interconnexion de type Buttery-Fat-Tree (BFT) [] est utilisée. La particularité de cette architecture est que chaque UMSB/DMSB de niveau N est connecté à 4 fois plus d’UMSB/DMSB de niveau N + 1. Par exemple, dans la guerre 2.7, un bloc logique configurable (ici LB) est connecté à un UMSB de même niveau (ici niveau 1). Cet UMSB sera donc connecté à quatre fois plus de UMSB (4 × 1 = 4 UMSB) de niveau N + 1 = 2, 16 UMSB de niveau 3… Enn les entrées/sorties sont regroupées dans un cluster spécifique et sont directement connectées aux UMSB/DMSB comme indiqué par la gure 2.7. Cette configuration permet donc de connecter ces plots à n’importe quel élément logique de l’architecture. Grâce à ce type d’architecture, une connexion entre deux blocs logiques nécessite moins de commutateurs comparée à l’architecture matricielle (mesh) car le nombre de commutateurs traversés augmente de façon logarithmique [44](contrairement à l’architecture matricielle où le nombre de commutateurs augmente linéairement en fonction de la distance de Manhattan entre deux blocs logiques). Xilinx et Altera commercialisent des FPGA avec des architectures hiérarchiques telles que Xilinx Virtex-II [71] et Altera Apex []. Au LIP6, une architecture arborescente multiniveaux appelée Multi-level FPGA (FPGA) [73] a été étudiée et montre un gain en surface de % comparé à une architecture matricielle.

Résumé |