Fundamentals of DC/DC converter

DC to DC converters are ubiquitous, from consumer electronics to electric vehicles. Such electronic devices often have multiple sub-circuits with their own supply level requirements different from the main input power which is either a built-in battery or an external supply. The supply of each sub-circuit can be either lower or higher than the main supply rail. Therefore, there are a lot of different types and topologies of DC/DC converter. They can be categorized into two main types: isolated and non-isolated. The isolated ones, as the name suggests, have their output isolated from the input with transformers. The benefits of this type are safety, noise isolation and floating output which are useful in some applications. However, the drawbacks of isolated DC/DC converters are big size, high cost and low efficiency. In the context of CPIO-SiP project, non-isolated type is preferable thanks to its higher efficiency, lower cost due to low number of components, and especially smaller size that favours high density designs. Table 1.1 details the typical non-isolated DC/DC converter topologies which are depicted in Figure 1.1. In order to support the topology reconfigurability in CPIO-SiP, the half-bridge structure is chosen as the switching unit (SU). One SU can operate as either synchronous buck or synchronous boost typology. Two SUs can be combined to form a four-switch buck-boost as outlined in Figure 1.2. The power router can be realized using MEMS (Micro Electro-Mechanical System) switches. These MEMS switches do not need to switch fast but they must support high current in on-state and high voltage in off-state.

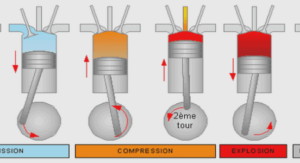

Why Gate Driver? Before the 1980s, the world of solid-state circuits witnessed the golden era of bipolar transistors (BJT) after they had replaced the vacuum tubes in radio and television. The power BJTs were robust but had a low current gain (beta) of <10 (White, 2018). Thus, a 10-A on-state requires at least 1-A continuous base current. Furthermore, the turn-off of BJTs demands a negative base current to remove all base-emitter charge. The fast turn-off hence needs a large negative current. There had been works addressing this issue such as Baker clamp and other feedback techniques. Since the 1980s, the MOSFETs had become more mature to replace the BTJs in power supplies as they have fast switching speed and required voltage drive instead of « base drive » current. In contrast to BJTs, MOSFETs do not require power input to maintain an ON or OFF-state. The gate capacitor, formed by the gate terminal, oxide layer and the active region, must be charged or discharged to switch the MOSFETs. The gate capacitor has to be charged to a certain required voltage, so-called threshold voltage (Vth), for the MOSFET to be ON.

Similarly, this charge must be depleted to turn the transistor off. When switching, MOSFETs do not instantly transit between the non-conducting and the conducting state. In fact, the transition time is inversely proportional to the charge and discharge speed of the gate capacitor, the typical range is from nanoseconds to milliseconds depending on power ratings and applications. Let’s examine an n-channel MOSFET driving a resistor in Figure 1.4. For simplicity, let’s consider this an ideal MOSFET with zero on-state resistance. The applied voltage VG to the gate rises from 0 V to surpass Vth to turn it ON. At t1, when VG equals Vth, the transistor starts to conduct and the drain current ID starts to rise from 0 A while VD starts to fall from Vin. At t2, when VD reaches 0 V, ID reaches it max value. The period [t1, t2] is called turn-on time of the MOSFET. During this time interval, the MOSFET consumes an energy (Eturn−on) as calculated in Equation 1.1. Since Vin and R are constant in the equation, the turn-on energy increases with ton. Therefore, faster turn-on results in lower switching loss. During turn-off transition, the MOSFET also exhibits a similar switching loss that depends on to f f . In order to control the ON and OFF interval of MOSFETs, a new class of circuit was born: Gate driver. A gate driver usually refers to a power amplifier that gets a signal from a controller (e.g. MCU or FPGA) and accordingly drives the gate of a power MOSFET, IGBT, SiC or GaN transistor.

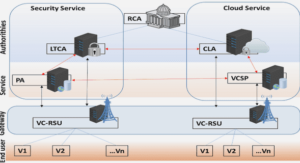

Gate Driver for GaN in literature To highlight the key elements in GaN gate drivers, Figure 2.2 shows the main building blocks in a gate driver for half-bridge topology, the most popular and commonly used converter topology (Delaine et al., 2012; Song et al., 2015). As depicted, there are two output stages controlling the two GaN devices, high-side (HS) and low-side (LS). Each of them has an independent power supply. The ground of HS logic is tied to VSW. To prevent large shoot-through current, a dead-time (DT) is usually inserted between the conduction time of HS and LS devices. The level shifter serves as the interface between LS logic and HS power domains. In the literature, the majority of GaN power modules in half-bridge still opt for system-in-package, which integrates GaN power device with silicon gate driver on a surface-mount package (Luo et al., 2014) or even PCB-level approaches. There are also works with discrete GaN devices in form of bare-die. As power converter circuits are downsized, switching frequency increases to cope with miniature inductors and capacitors. At high fPWM, timing mismatch between HS and LS becomes critical. Therefore, the performance bottleneck of high-speed gate drivers is the propagation delays of the level shifter and the DT generator. Such delays can be reduced with circuit techniques which leads to the classic power-speed compromise.

Conventional HV gate drivers often carry tens of ns of propagation delays in the level shifter, which becomes a critical problem as the fPWM reaches the 10 MHz range. In (Kawai et al., 2019), large delay of the level shifter and long DT in the driver limit its fPWM to 1 MHz. To reduce the total delay, which is dominated by the HV level shifter, a sub-ns delay bootstrapped gate driver with dynamic level shifter was reported (Song et al., 2015). The speed gained at the cost of high power consumption that limits the peak power efficiency. In a converter using half-bridge topology, the falling edge slope of VSW is proportional to the output current (Roschatt et al., 2016). A light load with a small DT leads to non-zero-switching of the GaN FETs whereas a heavy load with high DT results in reverse conduction in the GaN devices. Figure 2.3 illustrates the scenarios of optimal DT and two extremes. To overcome these challenges, digital control technique with generated adaptive DT is proposed. However, a high circuit complexity is involved (Wittmann et al., 2016). A near-optimal DT control is reported (Lee et al., 2011), however the long delay in sensing loop limits its use to low fPWM applications. In (Ke et al., 2016), a VSW dual-edge DT modulator was designed, which senses load current and supply voltage and then generates modulated delays for VSW rising and falling edges to adjust the instant DT, realizing zero-voltage switching for the GaN power switches. However, this method is too complicated for the CPIOS context of this project and the power consumption of the sub-ns comparator is high, leading to significant power loss.

Concerning the reliability, there have been some works addressing the bootstrap capacitor overcharge issue discussed in chapter 1. A Zener diode clamping technique was used to protect the bootstrap rail by sinking excessive charge to ground (Kawai et al., 2019; Song et al., 2015). However, this technique limits fPWM as the power loss is proportional to the switching frequency. In (Ke et al., 2016), an adaptive charging scheme called adaptive bootstrap balancing was proposed. To avoid overcharge, the charging time is initialized until the VSW zero-crossing sensor determines that the charge voltage has enter the safe zone. This technique involves a high degree of circuit complexity. Another reliability issue is current collapse in the GaN devices. This phenomenon is due to hot electron injection and charge trapping, having been widely considered as one of the major causes of GaN device aging and premature failure (Bahl et al., 2016). It degrades channel conductivity and increases Ron leading to higher junction temperature (TJ ). As a consequence, the mean time to failure (MTTF) decreases exponentially (Paine et al., 2019). To monitor the device aging, Ron drift is highly desirable as the early warning, because its change is directly related to current collapse effect. A similar approach was reported in (Smet et al., 2011) using VCE as the precursor for IGBTs. However, the monitoring can only be done when the system is off. An on-the-fly monitoring approach was reported (Dusmez et al., 2016) by using pole variation in loop gain for power MOSFETs which correlates to the Ron variation. However, this technique is limited in continuous conduction mode (CCM) and the implementation of pole location is very sophisticated. Another indirect Ron measurement technique is realized through an IGSS-inspired TJ sensor, based on the fact that gate-leakage IGSS of a GaN device is both TJ-sensitive and aging-independent (Chen & Ma, 2019a). With sensed TJ , the in-situ condition monitor removes the impact of TJ on Ron through the TJ dependence remover effectively. This technique allows to take more proactive measures to slow down the aging process whenever possible (Chen & Ma, 2019a).

INTRODUCTION |