Cours électricité circuits logiques programmables FPGA, tutoriel & guide de travaux pratiques en pdf.

Circuits logiques programmables FPGA

Les FPGA (abréviation anglaise de qui signifie réseau des portes programmables sur site) sont aussi des circuits logiques programmables par l’utilisateur. C’est une évolution des CLPD mais avec un concept différent, ils offrent un niveau d’intégration très élevé par rapport aux CPLD.

1) Structure des FPGA :

Un circuit FPGA contient un très grand nombre de macro cellules (environ 32*32 CLB) avec une très grande souplesse d’interconnexion entre eux. Dans le FPGA, le temps de propagation dans les couches logiques du circuit dépend de l’organisation et de la distance entre les macro cellules interconnectées.

2) Les ressources de FPGA :

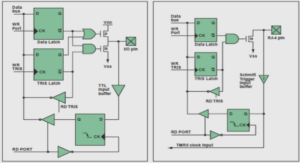

Entrées-sorties : elles sont indépendantes des macro cellules et de groupes de macro cellules. Elles ont comme élément de base la porte 3-états. Elles peuvent intégrer beaucoup des éléments comme le choix du temps de montée, l’incorporation d’une résistance de rappel à la tension d’alimentation pour fixer le niveau de tension d’une broche, le choix de type de sortie : soit collecteur ouvert, soit 3-états. Macro cellules : elles sont très nombreuses, et il n’y a pas de matrice ET et OU. La macro cellule est constituée d’une partie combinatoire et d’une partie séquentielle.

*La partie combinatoire permet de réaliser des fonctions de complexité moyenne. Les constructeurs ont proposé chacun une ou plusieurs solutions de synthèse dont les principales sont : La fonction de synthés à 4 ou 5 variables avec des portes classiques ET, OU et NON. La synthèse de fonctions à l’aide de multiplexeurs. La synthèse de fonctions combinatoires à l’aide de mémoire vive, on dit aussi réalisation des fonctions logiques par LUT, abréviation anglaise de « LOOKUP TABLE » signifiant table d’observation (ou de réalisation).

*La partie séquentielle comporte une ou deux bascules généralement de type D. il est rare de trouver des macro cellules uniquement pourvue de la partie combinatoire. Compte tenu de nombre de macro cellules et de leur structure, leur association permet la réalisation de n’importe quel autre type de bascule. Les macro cellules sont appelées :

Soit CLB : abréviation anglaise de « Configurable Logic Block », signifiant bloc Logique configurable. C’est la dénomination adoptée par Xilinx. Soit LC : abréviation anglaise de « Logic Cell », signifiant cellule logique, c’est le nom choisi par Cyprès. Soit LE : abréviation anglaise de « Logic Element, signifiant » élément logique, c’est l’appellation d’Altéra. La dénomination la plus courante pour désigner une macro cellule est CLB. A cet effet, on appelle souvent les FPGA, LCA, abréviation anglaise de « Logic Cell Array » signifiant réseau de cellules logiques. Cette dénomination des FPGA est dépassée comme marque Xilinx.